# CMOS TIA IS-54 Baseband Receive Port

**AD7013**

FEATURES

Single +5 V Supply

Receive Channel

Differential or Single-Ended Analog Inputs

Auxiliary Set of Analog I & Q Inputs

Two Sigma-Delta A/D Converters

Choice of Two Digital FIR Filters

Root-Raised-Cosine Rx Filters, α = 0.35

Brick Wall FIR Rx Filters

On-Chip or User Rx Offset Calibration

ADC Sampling Vernier

On-Chip or User Rx Offset Calibration

ADC Sampling Vernier

Three Auxiliary DACs

On-Chip Voltage Reference

Low Active Power Dissipation, Typical 45 mW

Low Sleep Mode Power Dissipation, <50 μW

# APPLICATIONS American TIA Digital Cellular Telephony American Analog Cellular Telephony Digital Baseband Receivers

### **GENERAL DESCRIPTION**

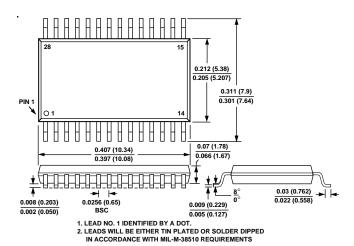

28-Pin SSOP

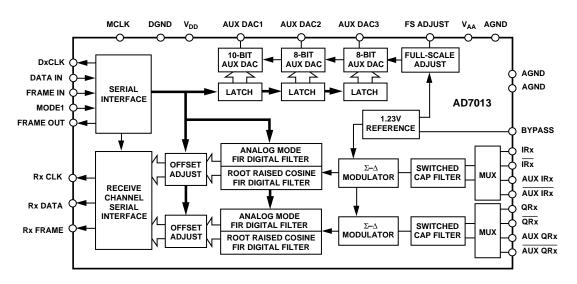

The AD7013 is a complete low power, CMOS, TIA IS-54 baseband receive port with single +5 V power supply. The part is

designed to perform the baseband conversion of I and Q waveforms in accordance with the American (TIA IS-54) Digital Cellular Telephone system.

The receive path consists of two high performance sigma-delta ADCs, each followed by a FIR digital filter. A primary and auxiliary set of IQ differential analog inputs are provided, where either can be selected as inputs to the sigma-delta ADCs. Also, a choice of two frequency responses are available for the receive FIR filters; a Root-Raised-Cosine filter for digital mode or a brick wall response for analog mode. Differential analog inputs are provided for both I and Q channels. On-chip calibration logic is also provided to remove either on-chip offsets or remove system offsets. A 16-bit serial interface is provided, interfacing easily to most DSPs. The receive path also provides a means to vary the sampling instant, giving a resolution to 1/32 of a symbol interval.

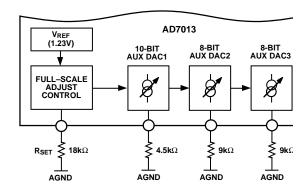

The auxiliary section provides two 8-bit DACs and one 10-bit DAC for functions such as automatic gain control (AGC), automatic frequency control (AFC) and power amplifier control.

As it is a necessity for all digital mobile systems to use the lowest possible power, the device has receive and auxiliary power down options. The AD7013 is housed in a space efficient 28-pin SSOP (Shrink Small Outline Package).

### FUNCTIONAL BLOCK DIAGRAM

# $\textbf{AD7013-SPECIFICATIONS}^{1} \ \ \overset{(V_{AA} = V_{DD} = +5 \text{ V} \pm 10\%; \text{ AGND} = DGND = 0 \text{ V}; \ \, f_{MCLK} = 6.2208 \text{ MHz}; } \\ T_{A} = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted)}$

| Parameter                           | AD7013A                          | Units            | Test Conditions/Comments                                       |

|-------------------------------------|----------------------------------|------------------|----------------------------------------------------------------|

| RECEIVE SECTION                     |                                  |                  |                                                                |

| ADC SPECIFICATION                   |                                  |                  |                                                                |

| Number of Input Channels            | 4                                |                  | (IRx–IRx) and                                                  |

|                                     |                                  |                  | $QRx-Q\overline{Rx}$ ; $CR12 = 0$                              |

|                                     |                                  |                  | (AUX IRx–AUX IRx) and                                          |

|                                     |                                  |                  | $(AUX QRx-\overline{AUX QRx}); CR12 = 1$                       |

| Number of ADC Channels              | 2                                |                  |                                                                |

| Resolution                          | 15                               | Bits             |                                                                |

| ADC Signal Range                    | 2.6                              | Volts p-p        | Measured Using an Input Sine Wave of 3 kHz                     |

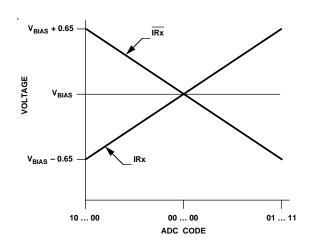

| Differential Signal Range           | $V_{BIAS} \pm 0.65$              | Volts            | For Both Noninverting and                                      |

|                                     |                                  |                  | Inverting Analog Inputs                                        |

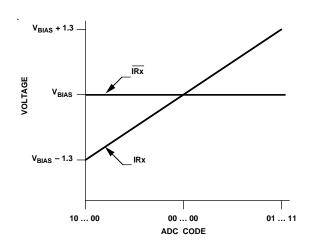

| Single-Ended Signal Range           | $V_{BIAS} \pm 1.3$               | Volts            | For Noninverting Analog Inputs;                                |

|                                     |                                  |                  | Inverting Analog Inputs = $V_{BIAS}$                           |

| $ m V_{BIAS}$                       | $0.65 \text{ to } (V_{AA}-0.65)$ | Volts min/max    | Differential                                                   |

|                                     | 1.3 to (V <sub>AA</sub> -1.3)    | Volts min/max    | Single-Ended                                                   |

| Input Range Accuracy                | ±7.5                             | %                |                                                                |

| Accuracy                            |                                  |                  |                                                                |

| Bias Offset Error                   | ±7.5                             | mV               | Autocalibration; V <sub>BIAS</sub> = min/max                   |

|                                     | ±55                              | mV               | User Calibration; I & Q Offset                                 |

| D                                   |                                  |                  | Adjust Registers Equal to Zero                                 |

| Dynamic Specifications              |                                  |                  |                                                                |

| CMRR                                | -40                              | dB typ           | Measured Using an Input Sine Wave of                           |

|                                     |                                  |                  | 3 kHz with Both Noninverting and                               |

| D : D                               | <b>5</b> 0                       | ID.              | Inverting Inputs Tied Together                                 |

| Dynamic Range                       | 70                               | dB typ           | Digital Mode Filter; CR11 = 0                                  |

| O. ID.3                             | 65                               | dB typ           | Analog Mode Filter; CR11 = 1                                   |

| $\mathrm{SNR}^2$                    | 65                               | dB min           | Digital Mode Filter; CR11 = 0                                  |

|                                     | 68                               | dB typ<br>dB min | Analog Mada Ellean CD11 = 1                                    |

|                                     | 60                               |                  | Analog Mode Filter; CR11 = 1                                   |

| Input Sampling Rate                 | 63<br>1.5552/1.28                | dB typ<br>MHz    | MCLK = 6.2208 MHz/5.12 MHz; MCLK/4                             |

| Output Word Rate                    | 97.2/80                          | kHz              | MCLK = 0.2208 MHz/5.12 MHz; MCLK/4 MCLK = 6.2208 MHz/5.12 MHz; |

| Output word Rate                    | 91.2/00                          | KIIZ             | $4 \times \text{Sampling of the Symbol Rate, MCLK/64}$         |

|                                     | 48.6/40                          | kHz              | MCLK = 6.2208 MHz/5.12 MHz;                                    |

|                                     | 10.0/10                          | NII              | 2 × Sampling of the Symbol Rate, MCLK/128                      |

|                                     |                                  |                  |                                                                |

| RECEIVE DIGITAL FILTERS             |                                  |                  |                                                                |

| Digital Mode                        |                                  |                  | MCLK = 6.2208 MHz                                              |

| Root-Raised-Cosine                  | $\alpha = 0.35$                  |                  |                                                                |

| Settling Time                       | 329.2                            | μs               |                                                                |

| Absolute Group Delay                | 164.6                            | μs               |                                                                |

| Frequency Response                  |                                  |                  |                                                                |

| 0-7.8975 kHz                        | ±0.05                            | dB max           |                                                                |

| 11.9 kHz                            | -3.0                             | dB               |                                                                |

| 16.4025 kHz                         | -19                              | dB               |                                                                |

| > 30 kHz                            | -66                              | dB max           | NOTE STORY                                                     |

| Analog Mode                         |                                  |                  | MCLK = 5.12 MHz                                                |

| Brick Wall Filter                   | 400                              |                  |                                                                |

| Settling Time                       | 400                              | μs               |                                                                |

| Absolute Group Delay                | 200                              | μs               |                                                                |

| Frequency Response<br>0–8 kHz       | 0 to 0 5                         | dD mar-          |                                                                |

| 0–8 KHZ<br>11.4 kHz                 | 0 to -0.5<br>-3.0                | dB max<br>dB     |                                                                |

| 11.4 kHz<br>15 kHz                  | -3.0<br>-24                      | dB<br>dB         |                                                                |

| 15 KHZ<br>>17 kHz                   |                                  | dB max           |                                                                |

| ~1 / KIIZ                           | -68                              | up max           |                                                                |

| TIA IS-54 RECEIVE SPECIFICATIONS    |                                  |                  |                                                                |

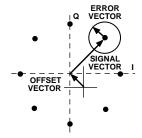

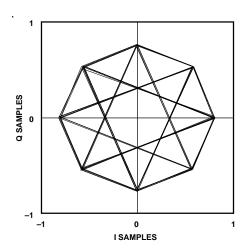

| Error Vector Magnitude <sup>3</sup> | 2                                | % rms typ        | Measured Using a Full-Scale Input                              |

| Error Offset Magnitude <sup>3</sup> | 1                                | % rms typ        |                                                                |

-2- REV. A

| Parameter                              |          | AD7013A              |            | Units                                   | Test Conditions/Comments                                       |

|----------------------------------------|----------|----------------------|------------|-----------------------------------------|----------------------------------------------------------------|

| AUXILIARY SECTION                      |          |                      |            |                                         |                                                                |

|                                        | AUX DAC1 | AUX DAC2             | AUX DAC3   |                                         |                                                                |

| Resolution                             | 10       | 8                    | 8          | Bits                                    |                                                                |

| DC Accuracy                            |          |                      | _          |                                         |                                                                |

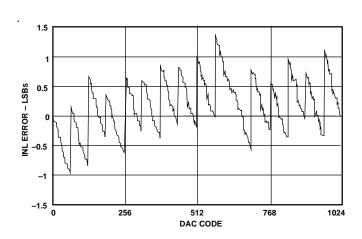

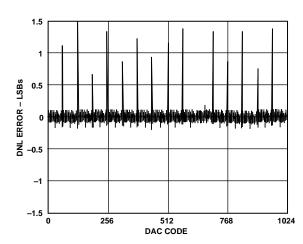

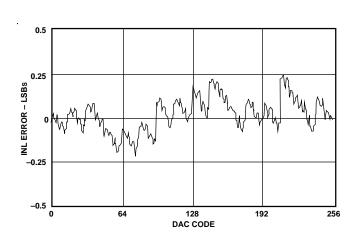

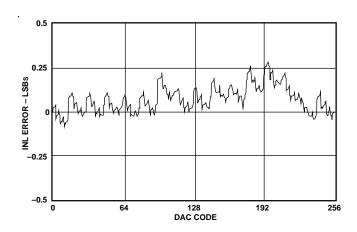

| Integral                               | ±3       | ±1                   | ±1         | LSBs max                                |                                                                |

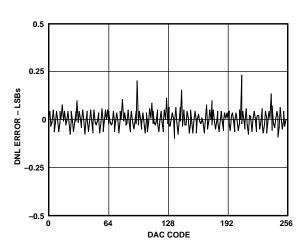

| Differential                           | -1.5/+4  | ±1                   | ±1         | LSBs max                                | AUX DAC2 & AUX DAC3 Guaranteed                                 |

| Differential                           | 1.5/14   | ± 1                  | <u>- 1</u> | Lobs max                                | Monotonic Monotonic                                            |

| Zero Code Leakage                      | ±500     | ±500                 | ±500       | nA max                                  | Wonotonic                                                      |

| Gain Error                             | ±7.5     | ±7.5                 | ±7.5       | % max                                   |                                                                |

| Output Full-Scale Current              |          |                      |            | /                                       | D = 10 1-0                                                     |

|                                        | 566      | 280                  | 280        | μA                                      | $R_{SET} = 18 \text{ k}\Omega$                                 |

| Output Impedance <sup>4</sup>          |          | 2                    |            | MΩ typ                                  |                                                                |

| Output Voltage Compliance              |          | 2.6                  |            | Volts max                               |                                                                |

| Coding                                 |          | Binary               |            |                                         |                                                                |

| Power Down Option                      |          | Yes                  |            |                                         |                                                                |

| REFERENCE SPECIFICATIONS               |          |                      |            |                                         |                                                                |

| V <sub>REF</sub>                       |          | 1.23                 |            | Volts typ                               |                                                                |

| Reference Accuracy                     |          | ±5                   |            | % max                                   |                                                                |

|                                        |          | 20                   |            |                                         |                                                                |

| Reference Impedance                    |          | 20                   |            | kΩ typ                                  |                                                                |

| LOGIC INPUTS                           |          |                      |            |                                         |                                                                |

| V <sub>INH</sub> , Input High Voltage  |          | $V_{ m DD}$ $-0.9$   |            | V min                                   |                                                                |

| V <sub>INL</sub> , Input Low Voltage   |          | 0.9                  |            | V max                                   |                                                                |

| I <sub>INH</sub> , Input Current       |          | 10                   |            | μA max                                  |                                                                |

| C <sub>IN</sub> , Input Capacitance    |          | 10                   |            | pF max                                  |                                                                |

|                                        |          |                      |            |                                         |                                                                |

| LOGIC OUTPUTS                          |          | *** 0.4              |            |                                         | IT   1 4 4 2 A                                                 |

| V <sub>OH</sub> , Output High Voltage  |          | $V_{ m DD}$ $\!-0.4$ |            | V min                                   | $ I_{\text{OUT}}  \le 40 \mu\text{A}$                          |

| V <sub>OL</sub> , Output Low Voltage   |          | 0.4                  |            | V max                                   | $ I_{OUT}  \le 1.6 \text{ mA}$                                 |

| POWER SUPPLIES                         |          |                      |            |                                         |                                                                |

| $ m V_{DD}$                            |          | 4.5/5.5              |            | V <sub>MIN</sub> /V <sub>MAX</sub>      |                                                                |

| $I_{\mathrm{DD}}^{5}$                  |          |                      |            | MIN MAX                                 |                                                                |

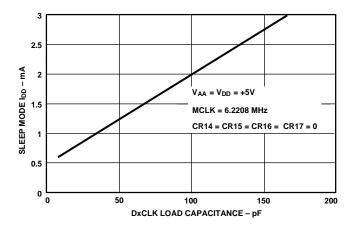

| All Sections Active                    |          | 10.5                 |            | mA max                                  | CR14 = CR15 = CR16 = CR17 = 1                                  |

|                                        |          | 9                    |            | mA typ                                  | MCLK = 6.2208 MHz; 80 pF                                       |

|                                        |          |                      |            |                                         | Load on DxCLK                                                  |

| ADCs Active Only                       |          | 8.6                  |            | mA max                                  | CR14 = 1; CR15 = CR16 = CR17 = 0                               |

| The do receive only                    |          | 0.0                  |            | 111111111111111111111111111111111111111 | MCLK = 6.2208 MHz; 80 pF                                       |

|                                        |          |                      |            |                                         | Load on DxCLK                                                  |

| ALIV DACO Action Contro                |          | 2.2                  |            | A                                       |                                                                |

| AUX DACs Active Only                   |          | 2.2                  |            | mA max                                  | CR14 = 0; CR15 = CR16 = CR17 = 1;                              |

| 10 Dis ALIV DAC A seissa               |          | 1.6                  |            | A                                       | MCLK Inactive, MCLK = 0 V<br>CR14 = CR15 = CR16 = 0; CR17 = 1; |

| 10-Bit AUX DAC Active                  |          | 1.6                  |            | mA max                                  |                                                                |

| All Cardiana D. I.D. 6                 |          | 0                    |            |                                         | MCLK Inactive, MCLK = 0 V                                      |

| All Sections Powered Down <sup>6</sup> |          | 2                    |            | mA max                                  | CR14 = CR15 = CR16 = CR17 = 0                                  |

|                                        |          |                      |            |                                         | MCLK = 6.2208 MHz; 80 pF                                       |

|                                        |          |                      |            |                                         | Load on DxCLK                                                  |

|                                        |          | 30                   |            | μA typ                                  | MCLK =100 kHz; 80 pF                                           |

|                                        |          |                      |            |                                         | Load on DxCLK                                                  |

|                                        |          | 10                   |            | μA max                                  | MCLK Inactive, MCLK = 0 V                                      |

### NOTES

Specifications subject to change without notice.

REV. A -3-

<sup>&</sup>lt;sup>1</sup>Operating temperature ranges as follows: A version: -40°C to +85°C. <sup>2</sup>SNR calculation includes noise and distortion components.

See Terminology.

Sampled tested only.

Measured while the digital inputs are static and equal to 0 V or V<sub>DD</sub>.

With all sections powered down, I<sub>DD</sub> is proportional to the capacitive load on DxCLK. For example, I<sub>DD</sub> is typically 1.7 mA with 80 pF load and 600 μA with 10 pF load.

### **TERMINOLOGY**

### **Sampling Rate**

This is the rate at which the modulators on the receive channels sample the analog input.

### **Output Rate**

This is the rate at which data words are made available at the RxDATA pin.

#### **Integral Nonlinearity**

This is the maximum deviation from a straight line passing through the endpoints of the DAC or ADC transfer function.

### **Differential Nonlinearity**

This is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the DAC or ADC.

#### **Dynamic Range**

Dynamic Range is the ratio of the maximum rms input signal to the rms noise of the converter, expressed logarithmically, in decibels  $(dB = 20 \log_{10} [ratio])$ .

### Signal to (Noise + Distortion) Ratio

This is the measured ratio of signal to (noise + distortion) at the output of the receive channel. The signal is the rms amplitude of the fundamental. Noise is the rms sum of all nonfundamental signals up to half the sampling frequency ( $f_{\rm s}/2$ ), excluding dc. The ratio is dependent upon the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical signal to (noise + distortion) ratio for a sine wave is given by:

Signal to (Noise + Distortion) = (6.02N + 1.76) dB

### **Settling Time**

This is the digital filter settling time in the AD7013 receive section.

### **Bias Offset Error**

This is the amount of offset in the receive channel ADC when the differential inputs are tied together.

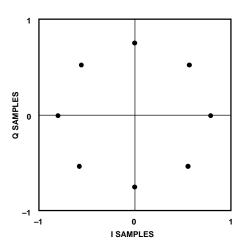

### Receive Error Vector Magnitude

This is a measure of the rms signal error vector introduced by the receive Root-Raised Cosine digital filter. This is measured by applying an ideal transmit signal (i.e., an ideal  $\pi/4$  DQPSK modulator and an ideal transmit Root-Raised Cosine filter) to the receive channel and measuring the resulting rms error vector.

### Offset Vector Magnitude

This is a measure of the offset vector introduced by the AD7013 as illustrated in the figure below. The offset vector is calculated so as to minimize the rms error vector for each of the constellation points.

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| $(T_A = +25^{\circ}C \text{ unless otherwise noted})$               |

|---------------------------------------------------------------------|

| $V_{AA}, V_{DD}$ to GND                                             |

| AGND to DGND0.3 V to +0.3 V                                         |

| Digital I/O Voltage to DGND0.3 V to $V_{DD}$ +0.3 V                 |

| Analog I/O Voltage to AGND $\ \dots \ -0.3\ V$ to $V_{DD}$ +0.3 $V$ |

| Operating Temperature Range                                         |

| Industrial (A Version)40°C to +85°C                                 |

| Storage Temperature Range65°C to +150°C                             |

| Maximum Junction Temperature+150°C                                  |

| SSOP $\theta_{JA}$ Thermal Impedance +122°C/W                       |

| Lead Temperature Soldering                                          |

| Vapor Phase (60 sec)+215°C                                          |

| Infrared (15 sec)+220°C                                             |

### NOTES

<sup>1</sup>Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions extended periods may affect device reliability.

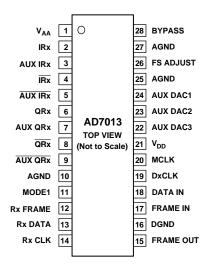

### PIN CONFIGURATION

### **ORDERING GUIDE**

| Model     | Temperature Range | Package Option* |

|-----------|-------------------|-----------------|

| AD7013ARS | −40°C to +85°C    | RS-28           |

$\star$ RS = SSOP.

### **CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this device features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### PIN FUNCTION DESCRIPTIONS

| SSOP Pin   |                          |                                                                                                                                                                                                                                                                                                                                                                 |

|------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number     | Mnemonic                 | Function                                                                                                                                                                                                                                                                                                                                                        |

| POWER SU   | PPLY                     |                                                                                                                                                                                                                                                                                                                                                                 |

| 1          | $V_{AA}$                 | Positive Power Supply for Analog section. A 0.1 µF decoupling capacitor should be connected between this pin and AGND.                                                                                                                                                                                                                                          |

| 21         | $ m V_{DD}$              | Positive Power Supply for Digital section. A 0.1 $\mu$ F decoupling capacitor should be connected between this pin and DGND. Both $V_{AA}$ and $V_{DD}$ should be externally tied together.                                                                                                                                                                     |

| 10, 25, 27 | AGND                     | Analog Ground.                                                                                                                                                                                                                                                                                                                                                  |

| 16         | DGND                     | Digital Ground. Both AGND and DGND should be externally tied together.                                                                                                                                                                                                                                                                                          |

| ANALOG SI  | IGNAL AND REFERENCE      |                                                                                                                                                                                                                                                                                                                                                                 |

| 28         | BYPASS                   | Reference Decoupling Output. A 10 nF decoupling capacitor should be connected between this pin and AGND.                                                                                                                                                                                                                                                        |

| 2, 4       | $IRx$ , $\overline{IRx}$ | Differential Analog Inputs for the I receive channel. These are the primary receive analog inputs and are selected by setting CR12 to a zero in the command register.                                                                                                                                                                                           |

| 6, 8       | $QRx$ , $\overline{QRx}$ | Differential Analog Inputs for the Q receive channel. These are the primary receive analog inputs and are selected by setting CR12 to a zero in the command register.                                                                                                                                                                                           |

| 3, 5       | AUX IRx, AUX IRx         | Auxiliary Differential Analog Inputs for the I receive channel. The Auxiliary inputs are selected by setting CR12 to a one in the command register.                                                                                                                                                                                                             |

| 7, 9       | AUX QRx, AUX QRx         | Auxiliary Differential Analog Inputs for the Q receive channel. The Auxiliary inputs are selected by setting CR12 to a one in the command register.                                                                                                                                                                                                             |

| 24         | AUX DAC1                 | Analog output from the 10-bit auxiliary DAC.                                                                                                                                                                                                                                                                                                                    |

| 3, 22      | AUX DAC2, AUX DAC3       | Analog outputs from the 8-bit auxiliary DACs.                                                                                                                                                                                                                                                                                                                   |

| 26         | FS ADJUST                | An external resistor is connected from this pin to ground to determine the full-scale current for AUX DAC1, AUX DAC2, and AUX DAC3.                                                                                                                                                                                                                             |

| SEDIAL INT | ΓERFACE AND CONTROL      |                                                                                                                                                                                                                                                                                                                                                                 |

| 20         | MCLK                     | Master Clock, Digital Input. When operating in IS-54 Digital mode this pin should be driven by a 6.2208 MHz CMOS compatible clock source and 5.12 MHz clock                                                                                                                                                                                                     |

| 19         | DxCLK                    | source for Analog Mode.  Transmit Clock, Digital Output. This is a continuous clock equal to MCLK/2 which can be used to clock the serial port of a DSP.                                                                                                                                                                                                        |

| 17         | FRAME IN                 | Digital Input. This is used to frame the clocking in of 16-bit words for the control registers serial interface.                                                                                                                                                                                                                                                |

| 18         | DATA IN                  | Digital Input. Transmit Serial Data, digital input. This pin is used to clock in data for the serial interface on the rising edge of DxCLK.                                                                                                                                                                                                                     |

| 15         | FRAME OUT                | Digital Output. This output represents a buffered version of FRAME IN and is controlled by the MODE1 pin. This pin can be used to daisy chain the FRAME IN signal.                                                                                                                                                                                              |

| 11         | MODE1                    | Digital Input. This pin determines the state of FRAME OUT. When MODE1 is high FRAME IN is buffered and made available on FRAME OUT. When MODE1 is low, FRAME OUT is in 3-STATE.                                                                                                                                                                                 |

| RECEIVE II | NTERFACE AND CONTROL     |                                                                                                                                                                                                                                                                                                                                                                 |

| 14         | RxCLK                    | Output Clock for the receive section interface.                                                                                                                                                                                                                                                                                                                 |

| 12         | RxFRAME                  | Synchronization output for framing I and Q data at the receive interface.                                                                                                                                                                                                                                                                                       |

| 13         | RxDATA                   | Receive Data, digital output. I and Q data are available at this pin via a 16-bit serial interface. Data is valid on the falling edge of RxCLK. I and Q data are clocked out as two 16-bits words, with the I word being clocked first. The last bit in each 16-bit word is a $I/\overline{Q}$ flag bit, indicating whether that word is an I word or a Q word. |

REV. A \_5\_

# $\begin{tabular}{ll} \textbf{CONTROL SERIAL INTERFACE TIMING}^1 & (V_{AA} = +5 \text{ V} \pm 10\%; V_{DD} = +5 \text{ V} \pm 10\%; AGND = DGND = 0 \text{ V}, \\ f_{MCLK} = 6.2208 \text{ MHz}; T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted}) \\ \end{tabular}$

| 50<br>5<br>5<br>0<br>0<br>-20<br>-20 | ns min ns min ns min ns min ns min ns max ns ns min | MCLK Cycle Time MCLK High Time MCLK Low Time MCLK Rising Edge to DxCLK Rising Edge Propagation Delay  DxCLK Cycle Time DxCLK Minimum High Time |

|--------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>)<br>)<br>)<br>-20              | ns min<br>ns min<br>ns max<br>ns<br>ns min          | MCLK Low Time MCLK Rising Edge to DxCLK Rising Edge Propagation Delay  DxCLK Cycle Time                                                        |

| )<br>)<br>-20                        | ns min<br>ns max<br>ns<br>ns min                    | MCLK Rising Edge to DxCLK Rising Edge Propagation Delay  DxCLK Cycle Time                                                                      |

| )<br>-20                             | ns max<br>ns<br>ns min                              | DxCLK Cycle Time                                                                                                                               |

|                                      | ns<br>ns min                                        | ,                                                                                                                                              |

| -20                                  | ns min                                              | ,                                                                                                                                              |

|                                      |                                                     | DxCLK Minimum High Time                                                                                                                        |

| -20                                  |                                                     |                                                                                                                                                |

|                                      | ns min                                              | DxCLK Minimum Low Time                                                                                                                         |

| 5                                    | ns min                                              | DxCLK Rising Edge to FRAME IN Setup Time                                                                                                       |

| )                                    | ns min                                              | DxCLK Rising Edge to FRAME IN Hold Time                                                                                                        |

| ót₅                                  | ns min                                              | FRAME IN Cycle Time                                                                                                                            |

| 5                                    | ns min                                              | DxCLK Rising Edge to DATA IN Setup Time                                                                                                        |

| )                                    | ns min                                              | DxCLK Rising Edge to DATA IN Hold Time                                                                                                         |

|                                      | ns min                                              | FRAME IN Rising Edge to FRAME OUT Rising Edge Propagation Delay                                                                                |

| 5                                    | ns max                                              |                                                                                                                                                |

| 5                                    | ns max                                              | MODE1 Low to FRAME OUT 3-STATE                                                                                                                 |

| 5                                    | ns max                                              | MODE1 High to FRAME OUT Active                                                                                                                 |

| 5                                    |                                                     | ns min<br>ns min<br>ns max<br>ns max                                                                                                           |

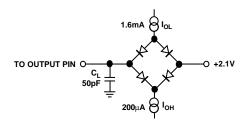

### NOTE

ti<sub>14</sub> is derived from the measured time taken by the FRAME OUT pin to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the 80 pF capacitor. This means that the time quoted in the Timing Characteristics is the

Figure 1. Load Circuit for Digital Outputs

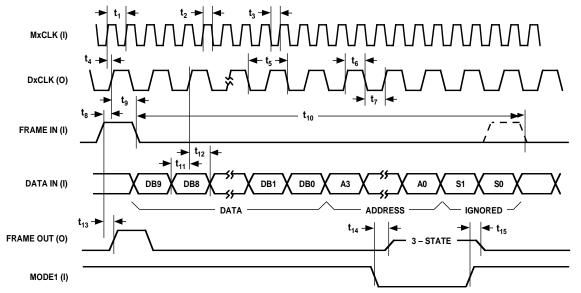

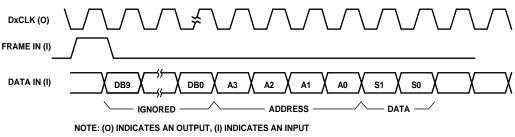

NOTE: (O) INDICATES AN OUTPUT, (I) INDICATES AN INPUT, MODE1 = LOGIC HIGH

Figure 2. 16-Bit Serial Interface for Writing to the AD7013 Internal Registers

# **RECEIVE SECTION TIMING** $(V_{AA} = +5 \text{ V} \pm 10\%; V_{DD} = +5 \text{ V} \pm 10\%; AGND = DGND = 0 \text{ V}, f_{MCLK} = 6.2208 \text{ MHz}; T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted})$

| Parameter       | Limit at $T_A = -40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ | Units  | Description                                                  |

|-----------------|---------------------------------------------------------------|--------|--------------------------------------------------------------|

| t <sub>16</sub> |                                                               |        | Power-Up Receive to RxCLK                                    |

| 10              | 10240t <sub>1</sub>                                           | ns max | CR13 = 0, Rx Offset Autocalibration On                       |

|                 | 6144t <sub>1</sub>                                            | ns max | CR13 = 1, Rx Offset Autocalibration Off                      |

| t <sub>17</sub> | 30                                                            | ns min | Propagation Delay from MCLK Rising Edge to RxCLK Rising Edge |

|                 | 85                                                            | ns max |                                                              |

| t <sub>18</sub> | 2t <sub>1</sub>                                               | ns     | RxCLK Cycle Time; CR10 = 1; 4× Sampling of the Symbol Rate   |

| t <sub>19</sub> | t <sub>1</sub> -20                                            | ns min | RxCLK High Pulse Width; CR10 = 1                             |

| t <sub>20</sub> | t <sub>1</sub> -20                                            | ns min | RxCLK Low Pulse Width; CR10 = 1                              |

| $t_{21}$        | -10                                                           | ns min | RxCLK Rising Edge to RxFRAME Rising Edge                     |

|                 | 10                                                            | ns max |                                                              |

| $t_{22}$        | 32t <sub>1</sub>                                              | ns     | RxFRAME Cycle Time; CR10 = 1                                 |

| t <sub>23</sub> | 2t <sub>1</sub>                                               | ns     | RxFRAME High Pulse Width; CR10 = 1                           |

| t <sub>24</sub> | -10                                                           | ns min | RxDATA Valid After RxCLK Rising Edge                         |

|                 | 10                                                            | ns max |                                                              |

| t <sub>25</sub> | 10t <sub>1</sub>                                              | ns min | DxCLK Rising Edge to Last Falling Edge RxCLK                 |

|                 | 64t <sub>1</sub>                                              | ns max |                                                              |

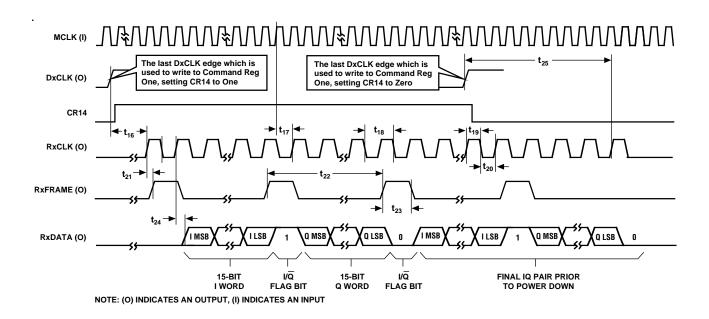

Figure 3. Receive Serial Interface Timing with 4× Sampling of the Symbol Rate (CR10 = 1)

REV. A \_7\_

# **RECEIVE SECTION TIMING** $(V_{AA}=+5~V\pm10\%;~V_{DD}=+5~V\pm10\%;~AGND=DGND=0~V,~f_{MCLK}=6.2208~MHz;~T_A=T_{MIN}~to~T_{Max},~unless~otherwise~noted)$

| Parameter       | Limit at $T_A = -40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ | Units  | Description                                                  |

|-----------------|---------------------------------------------------------------|--------|--------------------------------------------------------------|

| t <sub>26</sub> |                                                               |        | Power up Receive to RxCLK                                    |

| 20              | 10240t <sub>1</sub>                                           | ns max | CR13 = 0; Rx Offset Autocalibration On                       |

|                 | 6144t <sub>1</sub>                                            | ns max | CR13 = 1; Rx Offset autocalibration Off                      |

| t <sub>27</sub> | 30                                                            | ns min | Propagation Delay from MCLK Rising Edge to RxCLK Rising Edge |

|                 | 85                                                            | ns max |                                                              |

| t <sub>28</sub> | 4t <sub>1</sub>                                               | ns     | RxCLK Cycle Time; CR10 = 0; 2x Sampling of the Symbol Rate   |

| t <sub>29</sub> | 2t <sub>1</sub> -20                                           | ns min | RxCLK High Pulse Width; CR10 = 0                             |

| t <sub>30</sub> | 2t <sub>1</sub> -20                                           | ns min | RxCLK Low Pulse Width; CR10 = 0                              |

| t <sub>31</sub> | -10                                                           | ns min | RxCLK Rising Edge to RxFRAME Rising Edge                     |

|                 | +10                                                           | ns max | RxCLK to RxFRAME Propagation Delay                           |

| t <sub>32</sub> | 64t <sub>1</sub>                                              | ns     | RxFRAME Cycle Time; CR10 = 0                                 |

| t <sub>33</sub> | 4t <sub>1</sub>                                               | ns     | RxFRAME High Pulse Width; CR10 = 0                           |

| t <sub>34</sub> | -10                                                           | ns min | Propagation Delay from RxCLK Rising Edge to RxDATA Valid     |

|                 | +10                                                           | ns max |                                                              |

| t <sub>35</sub> | 12t <sub>1</sub>                                              | ns min | DxCLK Rising Edge to Last Falling Edge of RxCLK              |

|                 | 128t <sub>1</sub>                                             | ns max |                                                              |

| t <sub>36</sub> | $2t_1 + 20$                                                   | ns max | 3-State to Receive Channel Valid                             |

| t <sub>37</sub> | $2t_1 + 20$                                                   | ns max | Receive Channel to 3-State Relinquish Time                   |

$<sup>^{1}</sup>t_{37}$  is derived from the measured time taken by the receive channel outputs to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the 80 pF capacitor. This means that the time quoted in the Timing Characteristics is the true relinquish time of the part and as such is independent of external loading capacitance.

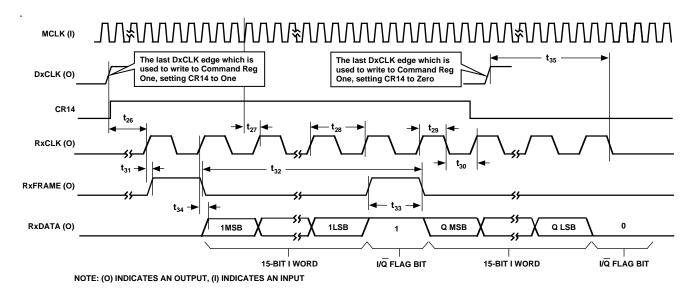

Figure 4. Receive Serial Interface Timing with 2× Sampling of the Symbol Rate (CR10 = 0)

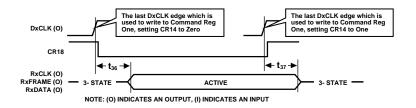

Figure 5. Receive Serial Interface 3-State Timing

–8– REV. A

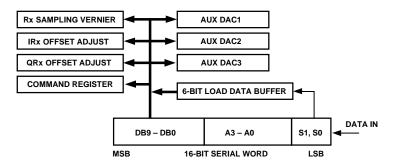

Figure 6. AD7013 Registers

Table I. Description and Address Map for AD7013 Internal Registers

| Register<br>Name | A3 | Add<br>A2 | lress<br>A1 | A0 | Register<br>Size | Reset<br>State | Description                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|------------------|----|-----------|-------------|----|------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| COMMAND          | 0  | 0         | 1           | 0  | 9 Bits           | All Zeros      | The COMMAND register is used to select various operating modes of the AD7013. A detailed description of the COMMAND register is given in Table II.                                                                                                                                                                                                                                   |  |  |

| VERNIER          | 0  | 1         | 0           | 0  | 4 Bits           | All Zeros      | The VERNIER register allows additional group delay to be introduced into the I and Q ADCs. This provides a means to vary the ADC sampling instant.                                                                                                                                                                                                                                   |  |  |

| IRx OFFSET       | 0  | 1         | 0           | 1  | 10 Bits          | All Zeros      |                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| QRx OFFSET       | 0  | 1         | 1           | 0  | 10 Bits          | All Zeros      | The contents of the QRx OFFSET register are substracted from the Q channel ADC word. When auto calibration is selected, this register is automatically loaded by the AD7013 at the beginning of a normal operation. When user calibration is selected this register can be externally loaded with a twos complement offset 10-bit word to be subtracted from subsequent ADC samples. |  |  |

| AUX DAC1         | 0  | 1         | 1           | 1  | 10 Bits          | All Zeros      | The 10-bit auxiliary DAC current output is determined by this register. The output current is equal to $\{AUX\ DAC1_{FULL\ SCALE}\ ^\star\ N/2^{10}\}$ where N is the 10-bit word contained in the AUX DAC1 register and AUX DAC1_{FULL\ SCALE} is determined by the value of $R_{SET}$ connected between FSADJUST and AGND.                                                         |  |  |

| AUX DAC2         | 1  | 0         | 0           | 0  | 8 Bits           | All Zeros      | The 8-bit auxiliary DAC current output is determined by this register. The output current is equal to {AUX DAC1 <sub>FULL SCALE</sub> * N/2 <sup>8</sup> } where N is the 8-bit word contained in the AUX DAC2 register and AUX DAC2 <sub>FULL SCALE</sub> is determined by the value of RSET connected between FS ADJUST and AGND.                                                  |  |  |

| AUX DAC3         | 1  | 0         | 0           | 1  | 8 Bits           | All Zeros      | The 8-bit auxiliary DAC current output is determined by this register. The output current is equal to $\{AUX\ DAC3_{FUIL\ SCALE} * N/2^8\}$ where N is the 8-bit word contained in the AUX DAC3 register and AUX DAC3_{FUIL\ SCALE} is determined by the value of $R_{SET}$ connected between FS ADJUST and AGND.                                                                    |  |  |

| RESET            | 0  | 0         | 0           | 1  | N/A              | N/A            | When this address in selected, all of the internal registers are initialized to their reset state.                                                                                                                                                                                                                                                                                   |  |  |

| 6-Bit LOAD       | 0  | 0         | 1           | 1  | N/A              | N/A            | When this address is used, a special loading sequence, as shown in Table IV, is used to write to any of the internal registers.                                                                                                                                                                                                                                                      |  |  |

| N/A              | 0  | 0         | 0           | 0  | N/A              | N/A            | No Action.                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| N/A              | 1  | 1         | 1           | 1  | N/A              | N/A            | No Action.                                                                                                                                                                                                                                                                                                                                                                           |  |  |

REV. A \_9\_

Figure 7. Internal AD7013 Registers

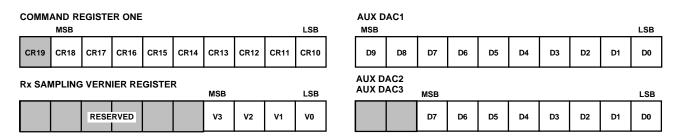

### Table II. Command Register One

| CR10 | = 0<br>= 1 | Low ADC sample rate. The sample rate of the receive ADCs are equal to $2\times$ the symbol rate or equal to MCLK/128. High ADC sample rate. The sample rate of the ADCs are equal to $4\times$ the symbol rate or equal to MCLK/64.                                                                                                                                                                                                                                                                                                                                                                                        |

|------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

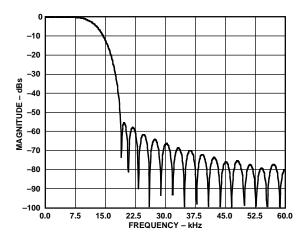

| CR11 | = 0        | RRC Receive FIR filter. This selects the root-raised consine filter response for the receive sigma-delta ADCs. This is used to match the transmit RRC filter as required by the IS-54 standard. The frequency response is shown in Figure 16.  Analog Mode FIR filter. This selects a filter response which has a sharper roll-off than the RRC FIR filter and the frequency response has also been scaled to operate at a master clock frequency of 5.12 MHz. This allows the sampling rate of the receive ADCs to be a multiple of 10 kHz as required for analog cellular. The frequency response is shown in Figure 17. |

| CR12 | = 0        | Primary ADC inputs. This selects IRx and $\overline{IRx}$ as the I channel inputs and QRx and $\overline{QRx}$ as the Q channel inputs.  Auxiliary ADC inputs. This selects AUX IRx and $\overline{AUX\ IRx}$ as the I channel inputs and AUX QRx and $\overline{AUX\ QRx}$ as the Q channel inputs.                                                                                                                                                                                                                                                                                                                       |

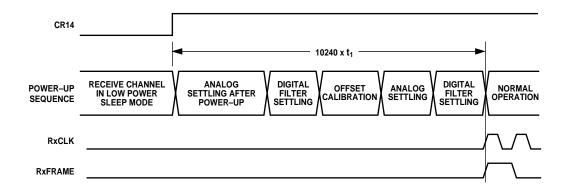

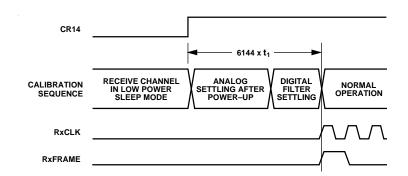

| CR13 | = 0        | Auto ADC offset calibration. If auto calibration is selected, then an offset word for both ADCs is calculated each time the receive ADCs are brought out of sleep mode. This allows ADC offsets within the AD7013 to be automatically calibrated out.  User ADC offset calibration. When user calibration is selected, then contents of the offset registers are not updated by the AD7013 when brought out of sleep mode. This allows the user to load the offset register externally thereby allowing the AD7013 to also calibrate out external offsets.                                                                 |

| CR14 | = 0<br>= 1 | Receive ADC sleep mode. This enters the I and Q ADCs into a low power sleep mode after outputting the current IQ sample.  Receive ADC active mode. This activates the receive ADCs for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CR15 | = 0<br>= 1 | 8-Bit AUX DAC3 sleep mode. This enters the 8-bit auxiliary DAC into a low power sleep mode. 8-Bit AUX DAC3 active mode. This activates the 8-bit auxiliary DAC for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CR16 | = 0<br>= 1 | 8-Bit AUX DAC2 sleep mode. This enters the 8-bit auxiliary DAC into a low power sleep mode 8-Bit AUX DAC2 active mode. This activates the 8-bit auxiliary DAC for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CR17 | = 0<br>= 1 | 10-Bit AUX DAC1 sleep mode. This enters the 10-bit auxiliary DAC into a low power sleep mode. 10-Bit AUX DAC1 active mode. This activates the 10-bit auxiliary DAC for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CR18 | = 0<br>= 1 | <ul><li>3-State Enable. This enables the 3-state buffers on the receive serial interface.</li><li>3-State Disable. This disables the 3-state buffers on the receive serial interface, entering the serial interface into 3-state.</li></ul>                                                                                                                                                                                                                                                                                                                                                                                |

| CR19 | = X        | No Action.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

-10- REV. A

### RECEIVE SECTION

The receive section consists of I and Q receive channels, each comprising of a simple switched-capacitor filter followed by a 15-bit sigma-delta ADC. The data is available on a 16-bit serial interface, interfacing easily to most DSPs. On-board digital filters, which form part of the sigma-delta ADCs, also perform system level filtering. A choice of two digital filter responses are available, optimized for either  $\pi/4$  DQPSK digital mode or the existing analog cellular system. For digital mode, Root-Raised Cosine digital filters can be selected; whereas for analog mode, digital filters with a -3 dB point of 11.4 kHz can be selected. Their amplitude and phase response characteristics provide excellent adjacent channel rejection. A means is also provided to calibrate either on-chip or receive path offsets in both the I and Q channels. The receive section is also provided with a low power sleep mode, drawing only minimal current between receive bursts.

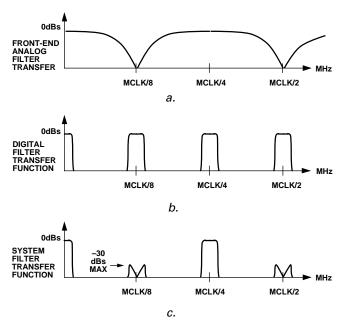

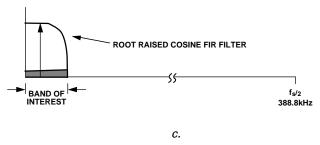

### **Switched Capacitor Input**

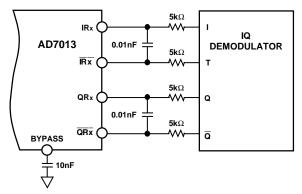

The receive section analog front-end is sampled at MCLK/4 by a switched-capacitor filter. The filter has a zero at MCLK/8 as shown in Figure 8a. The receive channel also contains a digital low-pass filter (further details are contained in the following section) which operates at a clock frequency of MCLK/8. Due to the sampling nature of the digital filter, the pass band is repeated about the operating clock frequency (MCLK/8) and at multiples of the clock frequency (Figure 8b). Because the first null of the switched-capacitor filter coincides with the first image of the digital filter, this image is attenuated by an additional 30 dBs (Figure 8c) further simplifying the external antialiasing requirements. A simple R-C Network can be used to attenuate the digital filter image at MCLK/8 as shown in Figure 9.

Figure 8. Switched Capacitor and Digital Filter Transfer Functions

### **Receive Channel Differential Inputs**

The receive channel uses differential inputs to interface more easily to IQ demodulators and also to provide common-mode noise rejection. However, if required the receive channel inputs can also be configured for single ended operation. The primary and auxiliary channels have similar performance and either can be used for differential operation or single-ended operation. The CR12 control bit determines whether the primary or auxiliary inputs are connected to the differential inputs of the sigma-delta modulator.

Figure 9 illustrates an antialiasing filter comprised of a single pole RC network with a –3 dB frequency of 159 kHz. The low-pass filter provides sufficient rejection at images of the FIR digital filter illustrated in Figure 10c.

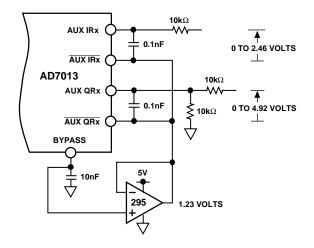

For single ended operation, the inverting input should be connected to a bias voltage and the noninverting input should swing  $\pm 1.3$  V around this bias voltage in order to exercise the entire ADC range. In applications where the full  $\pm 1.3$  V range is not required, the on-chip 1.23 V reference can be used to provide the bias voltage. For instance as in Figure 10, an OP295 rail-to-rail low power op amp is used to buffer the BYPASS pin in order to generate a 1.23  $V_{\rm BIAS}$ . The  $V_{\rm BIAS}$  is connected to the inverting input thereby setting the single-ended input range equal to 0 V to 2.46 V. Also with the addition of an attenuator circuit the input range can be expanded to 0 V to 4.92 V as shown on the second ADC channel. If the inverting input is tied to AGND, then only half the ADC range is available.

Figure 9. External RC Network for Differential Signals

Figure 10. External RC Network for Single-Ended Signals

REV. A –11–

Figure 11. ADC Transfer Function for Differential Operation

Figure 12. ADC Transfer Function for Single-Ended Operation

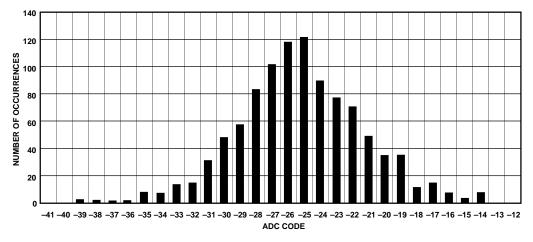

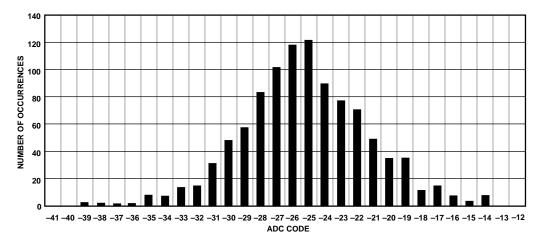

### SIGMA-DELTA ADC

The AD7013 receive channels employ a sigma-delta conversion technique, which provides a high resolution 15-bit output for both I and Q channels with system filtering being implemented on-chip.

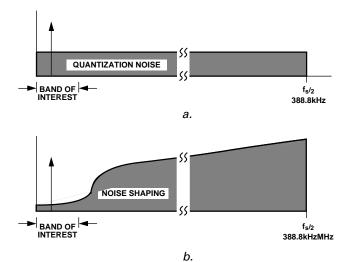

The output of the switched-capacitor filter is continuously sampled at MCLK/8, by a charge-balanced modulator, and is converted into a digital pulse train whose duty cycle contains the digital information. Due to the high oversampling rate which spreads the quantization noise from 0 to  $f_s/2$ , the noise energy which is contained in the band of interest is reduced (Figure 13a). To reduce the quantization noise still further, a high order modulator is employed to shape the noise spectrum, so that most of the noise energy is shifted out of the band of interest (Figure 13b).

The digital filter that follows the modulator removes the large out of band quantization noise (Figure 13c), while converting the digital pulse train into parallel 15-bit wide binary data. The 15-bit I and Q data plus an I/Q flag bit is made available, via a serial interface, as a 16-bit word, MSB first.

Figure 13. a. Effect of High Oversampling Ratio. b. Use of Noise Shaping to Further Improve SNR. c. Use of Digital Filtering to Remove the Out of Band Quantization Noise

### Digital Filter

The digital filters used in the AD7013 receive section carry out two important functions. First, they remove the out of band quantization noise which is shaped by the analog modulator. Second, they are also designed to perform system level filtering, providing the Root-Raised Cosine filter as required for TIA IS-54.

Since digital filtering occurs after the A/D conversion process, it can remove noise injected during the conversion process. Analog filtering cannot do this. Also, the digital filter combines low passband ripple with a steep roll off, while also maintaining a linear phase response. This is very difficult to achieve with analog filters.

### Filter Characteristics

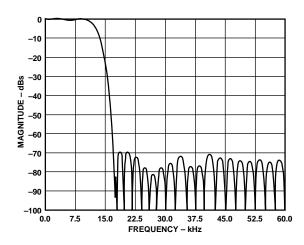

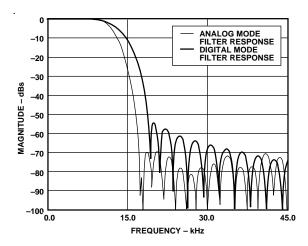

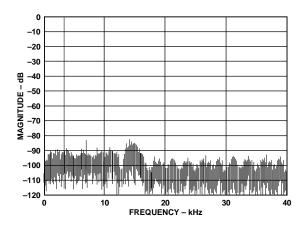

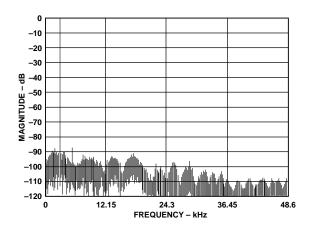

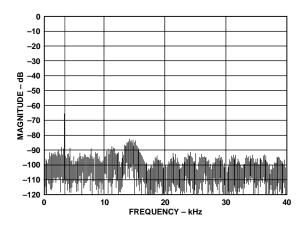

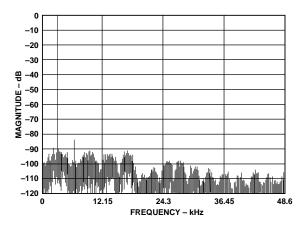

The digital filter is a 256-tap FIR filter, clocked at 1/8 the master clock frequency. A choice of two frequency responses are available: a Root-Raised Cosine response (CR11 = 0) and a brick wall response at 11.4 kHz (CR11 = 1) for analog mode. Figure 16 and Figure 17 illustrate the respective frequency responses for both digital mode and analog mode while Figure 18 compares the low frequency response of the digital filters.

Due to the low-pass nature of the receive filters there is a settling time associated with step input functions. Output data will not be meaningful until all the digital filter taps have been loaded with data samples taken after the step change. Hence, the AD7013 digital filters have a settling time of  $256 \times 8t_1$  (i.e., 329.2 µs when MCLK = 6.2208 MHz and 400 µs when MCLK = 5.12 MHz).

Figure 14. Autocalibration Routine After Exiting Low Power Sleep Mode

Figure 15. User-Calibration Routine After Exiting Low Power Sleep Mode

REV. A –13–

Figure 16. Receive Root Raised Cosine FIR Filter; CR11 = 0, MCLK = 6.2208 MHz

Figure 17. Receive Analog Mode FIR Filter; CR11 = 1, MCLK = 5.12 MHz

Figure 18. Comparision of the Two Frequency Responses Where Digital Mode was Clocked at 6.2208 MHz and Analog Mode was Clocked at 5.12 MHz

### **Receive Offset Calibration**

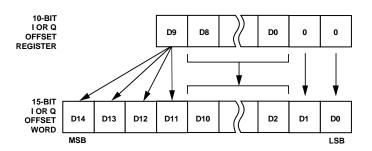

Included in the digital filter is a means by which receive signal offsets may be calibrated out. Each channel of the digital low-pass filter section has an offset register. The offset register can be made to contain a value representing the dc offset of the preceding analog circuitry. In normal operation, the value stored in the offset register is subtracted from the filter output data before the data appears on the serial output pin. By so doing, dc offsets in the I and Q channels get calibrated out. Autocalibration or user calibration can be selected. Autocalibration will remove internal offsets only while user calibration allows the user to write to the offset register in order to also remove external offsets.

The offset registers have enough resolution to hold the value of any dc offset between  $\pm 153$  mV (1/8th of the input range). The 10-bit offset register represents a twos-complement value which is mapped to a 15-bit twos-complement word as shown in Figure 19. The contents of the offset registers are subtracted from their respective ADC samples.

Figure 19. Position of the 10-Bit Offset Word Within the 15-Bit ADC Word

Receive Offset Adjust: Auto-Calibration (CR13 = 0)

If receive autocalibration has been selected (CR13 = 0), then the AD7013 will initiate an autocalibration routine each time the receive path is brought out of the low power sleep mode (CR14 = 0). The AD7013 internally disconnects the differential inputs from the input pins and shorts the differential inputs to measure the resulting ADC offset. This is then averaged 16 times to reduce ADC noise, and the averaged result is then placed in the offset register. The input to the ADC is then switched back for normal operation, and after allowing for both analog settling and digital filter settling, the first IQ sample pair is output (Figure 14). Autocalibration will only remove on-chip offsets.

Receive Offset Adjust: User Calibration (CR13 = 1)

When user calibration has been selected, the receive offset register can be written to, allowing offsets in the IF/RF demodulation circuitry to be also calibrated out. However, the user is now responsible for calibrating out receive offsets belonging to the AD7013. When the receive path enters the low power mode (CR14 = 0), the offset registers remain valid. After powering up, the first IQ sample pair is output once time has elapsed for both the analog circuitry to settle and also for the output of the digital filter to settle as shown in Figure 15.

-14- REV. A

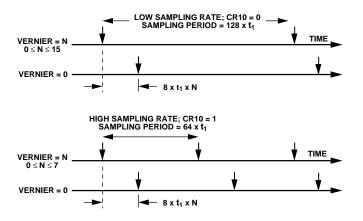

### ADC Sampling Vernier

Also included in the digital filter is the means to vary the sampling instant, as Figure 20 illustrates. The absolute group delay can be varied from a minimum of four symbols to a maximum of four and a half symbols allowing the user to define the sampling instant to a resolution 1/32 of the symbol rate. The vernier can be used to seek the optimum sampling instant for minimum Inter-Symbol-Interference (ISI).

Figure 20. I and Q ADC Sampling Vernier for  $2 \times$  the Symbol Rate and  $4 \times$  the Symbol Rate

A 4-bit vernier register is used to set the sampling instant for both the I and Q receive ADCs. When the vernier register is programmed with zero the ADCs will have a minimum group delay of approximately 165  $\mu s$ . Nonzero values in the vernier register will add additional group delay thereby moving the sampling instant for both ADCs. After programming the sampling vernier it takes eight symbols (\$\approx 330 \mu s) for the digital filter to settle. When the ADC is operating at the high rate, vernier values from 8 to 15 yield similar sampling instants as vernier values from 0 to 7, but delayed by an additional 1/4 of a symbol period.

Table III. Loading Sequence for the 16-Bit Interface

| DB9-DB0 | A3-A0               | S1, S0  | Action                |

|---------|---------------------|---------|-----------------------|

| D9-D0   | Destination Address | Ignored | Destination Reg←D9–D0 |

Table IV. Loading Sequence for the 6-Bit Interface

| DB9-DB0 | A3-A0               | S1, S0 | Action                |

|---------|---------------------|--------|-----------------------|

| Ignored | 0011                | D9, D8 | D9←S1 and D8←S0       |

| Ignored | Destination Address | D7, D6 | D7←S1 and D6←S0       |

| Ignored | Destination Address | D5, D4 | D5←S1 and D4←S0       |

| Ignored | Destination Address | D3, D2 | D3←S1 and D2←S0       |

| Ignored | Destination Address | D1, D0 | D1←S1 and D0←S0       |

|         |                     |        | Destination Reg←D9-D0 |

Receive Section Digital Interface

The receive interface can be connected to DSP processors requiring the use of only one serial port. The 15-bit I and Q samples are made available as 16-bit words, where the last bit in each word is an I/Q flag bit.

The serial data is made available on the RxDATA pin, with the I/Q flag indicating whether the 16-bit word being clocked out is an I sample or a Q sample. Although the I data is clocked out before the Q data, internally both samples are processed together. The receive interface (RxCLK, RxFRAME & RxDATA) can be 3-Stated by setting CR18 to zero, CR18 should be set high for normal operation.

When the receive section is put into sleep mode, by setting CR14 to zero, the receive interface will complete the current IQ cycle before entering into a low power sleep mode.

High Sampling Rate (CR10 =1)

The timing diagram for the receive interface is shown in Figure 3. The output word rate per channel is equal to 97.2 kHz (MCLK/64) which corresponds to 4 times the symbol rate.

When the receive section is brought out of sleep mode (CR14 = 1), the receive section will initiate an offset autocalibration routine if CR13 = 0. Once the receive offset calibration routine is complete then RxCLK will continuously shift out I and Q data, always beginning with I data. RxFRAME provides a framing signal that is used to indicate the beginning of an I or Q, 16-bit data word that is valid on the next falling edge of RxCLK. On coming out of sleep, RxFRAME goes high one clock cycle before the beginning of I data, and subsequently goes high in the same clock cycle as the last bit of each 16-bit word (both I and Q). RxDATA is valid on the falling edge of RxCLK and is clocked out MSB first, with the I/Q flag bit indicating whether the 16-bit word is an I sample or a Q sample.

Figure 21. 6-Bit Serial Interface for Internal AD7013 Registers

REV. A –15–

Low Sampling Rate (CR10 = 0)

The timing diagram for the receive interface is shown in Figure 4. The output word rate per channel is equal to 48.6 kHz (MCLK/128) which corresponds to two times the symbol rate. The low sampling rate operates in a similar manner to that described for the high sampling rate.

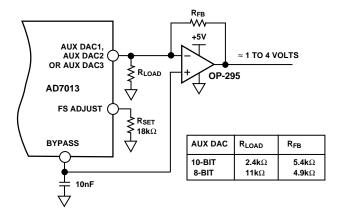

### **AUXILIARY DACs**