# SMJ320VC5416 Fixed-Point Digital Signal Processor

# Data Manual

Literature Number: SGUS035A April 2003 - Revised July 2003

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

On products compliant to MIL-PRF-38535, all parameters are tested unless otherwise noted. On all other products, production processing does not necessarily include testing of all parameters.

# **REVISION HISTORY**

| REVISION | DATE       | PRODUCT STATUS  | HIGHLIGHTS    |

|----------|------------|-----------------|---------------|

| *        | March 2003 | Production Data | Original      |

| А        | July 2003  | Production Data | Limit changes |

|          |            |                 |               |

|          |            |                 |               |

|          |            |                 |               |

|          |            |                 |               |

|          |            |                 |               |

|          |            |                 |               |

|          |            |                 |               |

|          |            |                 |               |

|          |            |                 |               |

|          |            |                 |               |

|          |            |                 |               |

|          |            |                 |               |

|          |            |                 |               |

|          |            |                 |               |

|          |            |                 |               |

|          |            |                 |               |

# **Contents**

| Se | ection |          |                                                  | Page |

|----|--------|----------|--------------------------------------------------|------|

| 1  | SMJ32  | 20VC5416 | Features                                         | 1    |

| 2  | Introd | uction   |                                                  | 2    |

|    | 2.1    | Descript | ion                                              | 2    |

|    | 2.2    | •        | gnments                                          |      |

|    |        | 2.2.1    | Pin Assignments for the HFG Package              |      |

|    | 2.3    |          | Descriptions                                     |      |

| 3  |        | -        | rview                                            |      |

| •  | 3.1    |          |                                                  |      |

|    | 0.1    | 3.1.1    | Data Memory                                      |      |

|    |        | 3.1.2    | Program Memory                                   |      |

|    |        | 3.1.3    | Extended Program Memory                          |      |

|    | 3.2    |          | ROM With Bootloader                              |      |

|    | 3.3    | •        | RAM                                              |      |

|    | 3.4    | •        | Memory Security                                  |      |

|    | 3.5    |          | Map                                              |      |

|    | 3.3    | 3.5.1    | Relocatable Interrupt Vector Table               |      |

|    | 0.6    |          | •                                                |      |

|    | 3.6    |          | Peripherals                                      |      |

|    |        | 3.6.1    | Software-Programmable Wait-State Generator       |      |

|    |        | 3.6.2    | Programmable Bank-Switching                      |      |

|    | 0.7    | 3.6.3    | Bus Holders                                      |      |

|    | 3.7    |          | I/O Ports                                        |      |

|    |        | 3.7.1    | Enhanced 8-/16-Bit Host-Port Interface (HPI8/16) |      |

|    |        | 3.7.2    | HPI Nonmultiplexed Mode                          |      |

|    | 3.8    |          | nnel Buffered Serial Ports (McBSPs)              |      |

|    | 3.9    |          | re Timer                                         |      |

|    | 3.10   |          | enerator                                         |      |

|    | 3.11   |          | ed External Parallel Interface (XIO2)            |      |

|    | 3.12   |          | ontroller                                        |      |

|    |        | 3.12.1   | Features                                         |      |

|    |        | 3.12.2   | DMA External Access                              |      |

|    |        | 3.12.3   | DMA Memory Map                                   |      |

|    |        | 3.12.4   | DMA Priority Level                               |      |

|    |        | 3.12.5   | DMA Source/Destination Address Modification      |      |

|    |        | 3.12.6   | DMA in Autoinitialization Mode                   |      |

|    |        | 3.12.7   | DMA Transfer Counting                            |      |

|    |        | 3.12.8   | DMA Transfer in Doubleword Mode                  | 32   |

|    |        | 3.12.9   | DMA Channel Index Registers                      | 32   |

|    |        | 3.12.10  | DMA Interrupts                                   |      |

|    |        | 3.12.11  | DMA Controller Synchronization Events            |      |

|    | 3.13   | General- | -Purpose I/O Pins                                | 34   |

|    |        | 3.13.1   | McBSP Pins as General-Purpose I/O                |      |

|    |        | 3.13.2   | HPI Data Pins as General-Purpose I/O             |      |

|    | 3.14   | Device I | D Register                                       | 35   |

|    | 3.15   | Memory-  | -Mapped Registers                                | 35   |

|    | 3.16   |          | Control Registers and Subaddresses               |      |

|    | 3.17   |          | bbank Addressed Registers                        |      |

|    |        |          |                                                  |      |

|   | 3.18     | Interrupt  | S                                                                   | 41 |

|---|----------|------------|---------------------------------------------------------------------|----|

| 4 | Docum    | nentation  | Support                                                             | 42 |

| 5 | Electri  | cal Speci  | fications                                                           | 43 |

|   | 5.1      | Absolute   | Maximum Ratings                                                     | 43 |

|   | 5.2      | Recomm     | nended Operating Conditions                                         | 43 |

|   | 5.3      | Electrica  | I Characteristics Over Recommended Operating Case Temperature Range |    |

|   |          | (Unless    | Otherwise Noted)                                                    |    |

|   | 5.4      | -          | Thermal Resistance Characteristics                                  |    |

|   | 5.5      |            | arameter Symbology                                                  |    |

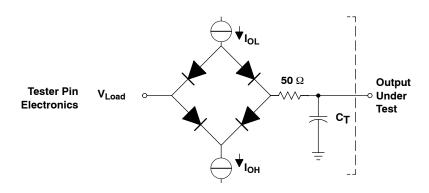

|   | 5.6      | Internal ( | Oscillator With External Crystal                                    | 45 |

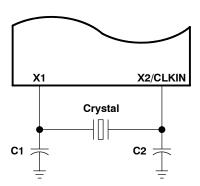

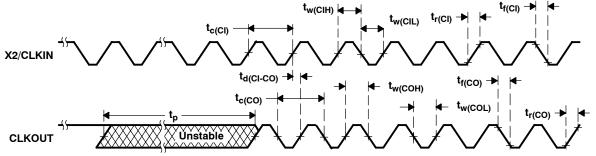

|   | 5.7      | Clock Op   | otions                                                              | 46 |

|   |          | 5.7.1      | Divide-By-Two and Divide-By-Four Clock Options                      | 46 |

|   |          | 5.7.2      | Multiply-By-N Clock Option (PLL Enabled)                            | 48 |

|   | 5.8      | Memory     | and Parallel I/O Interface Timing                                   | 49 |

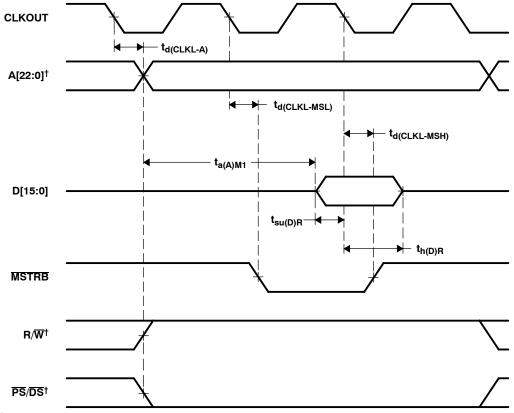

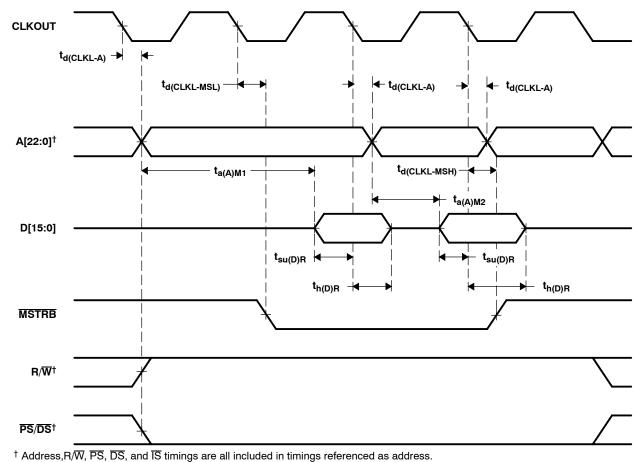

|   |          | 5.8.1      | Memory Read                                                         | 49 |

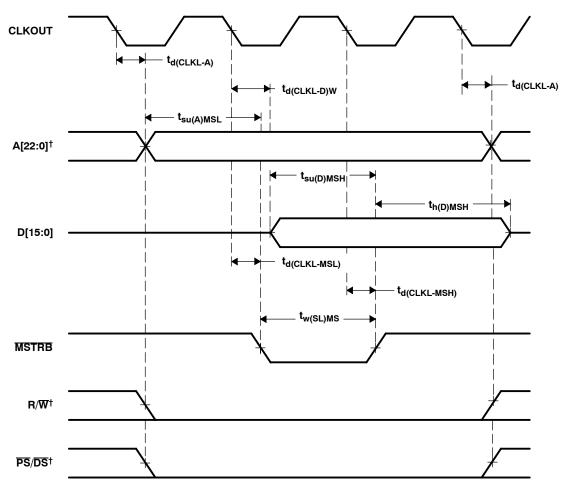

|   |          | 5.8.2      | Memory Write                                                        | 52 |

|   |          | 5.8.3      | I/O Read                                                            | 53 |

|   |          | 5.8.4      | I/O Write                                                           | 54 |

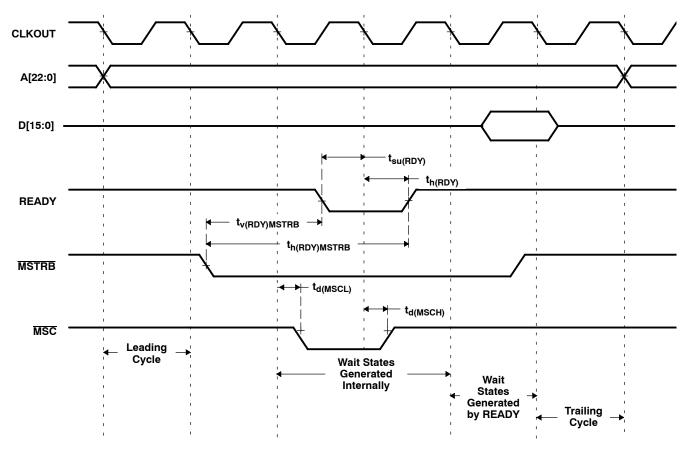

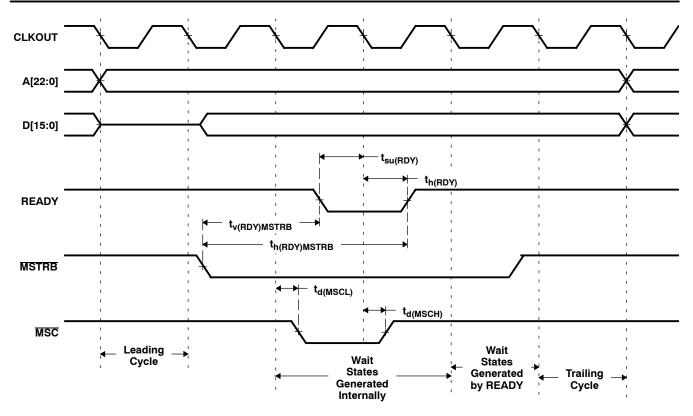

|   | 5.9      | Ready T    | iming for Externally Generated Wait States                          | 55 |

|   | 5.10     | -          | nd HOLDA Timings                                                    |    |

|   | 5.11     |            | IO, Interrupt, and MP/MC Timings                                    |    |

|   | 5.12     |            | on Acquisition (IAQ) and Interrupt Acknowledge (IACK) Timings       |    |

|   | 5.13     |            | Flag (XF) and TOUT Timings                                          |    |

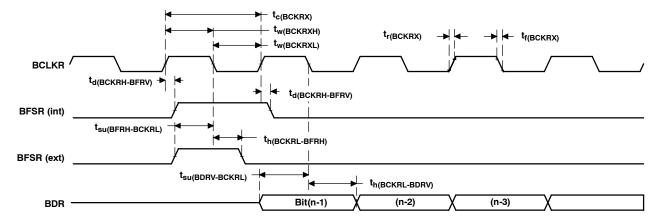

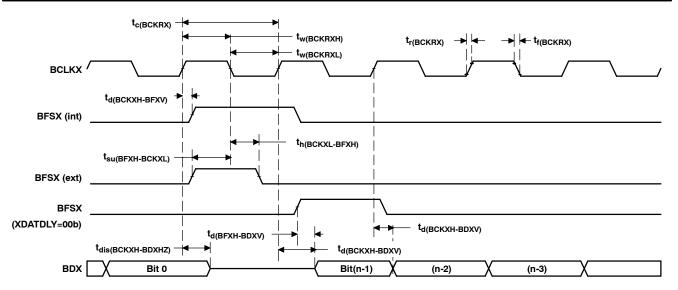

|   | 5.14     |            | nnel Buffered Serial Port (McBSP) Timing                            |    |

|   |          | 5.14.1     | McBSP Transmit and Receive Timings                                  |    |

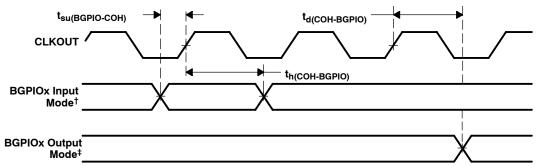

|   |          | 5.14.2     | McBSP General-Purpose I/O Timing                                    |    |

|   |          | 5.14.3     | McBSP as SPI Master or Slave Timing                                 |    |

|   | 5.15     |            | rt Interface Timing                                                 |    |

|   |          | 5.15.1     | HPI8 Mode                                                           |    |

|   |          | 5.15.2     | HPI16 Mode                                                          |    |

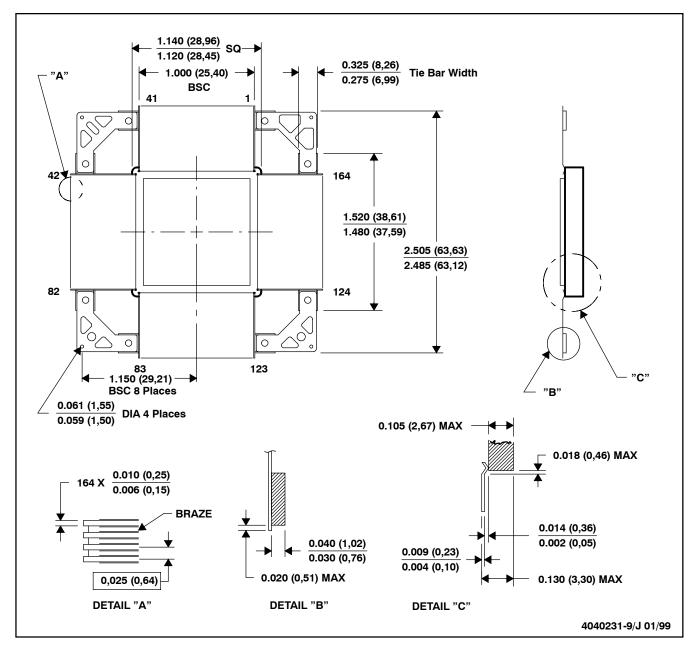

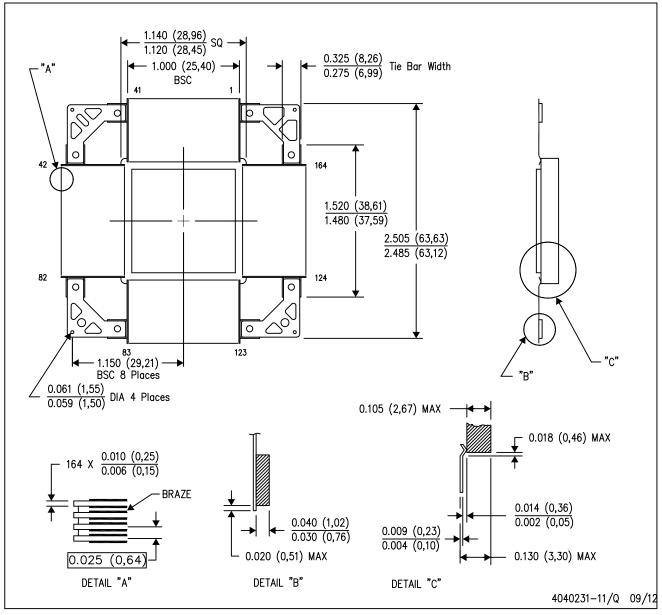

| 6 | Mecha    |            | a                                                                   |    |

| - | 6.1      |            | Quad Flatpack Mechanical Data                                       |    |

|   | <b>U</b> | 20.41110   |                                                                     |    |

# **List of Figures**

| Figure                                                                                 | Page |

|----------------------------------------------------------------------------------------|------|

| 2-1. 164-Pin HFG Ceramic Quad Flatpack (Top View)                                      | 4    |

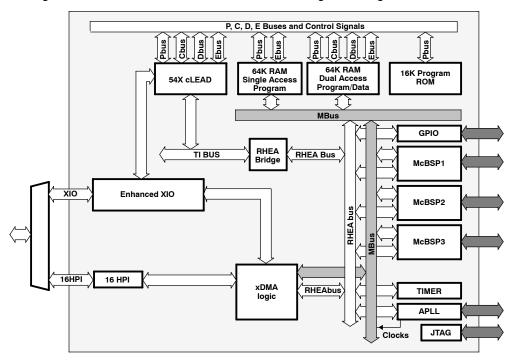

| 3-1. SMJ320VC5416 Functional Block Diagram                                             | 10   |

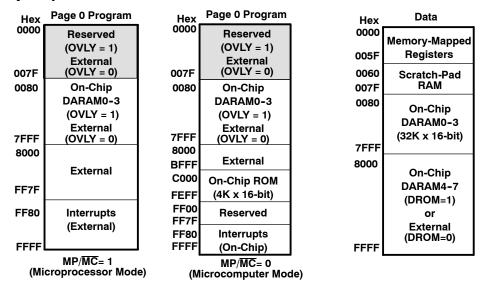

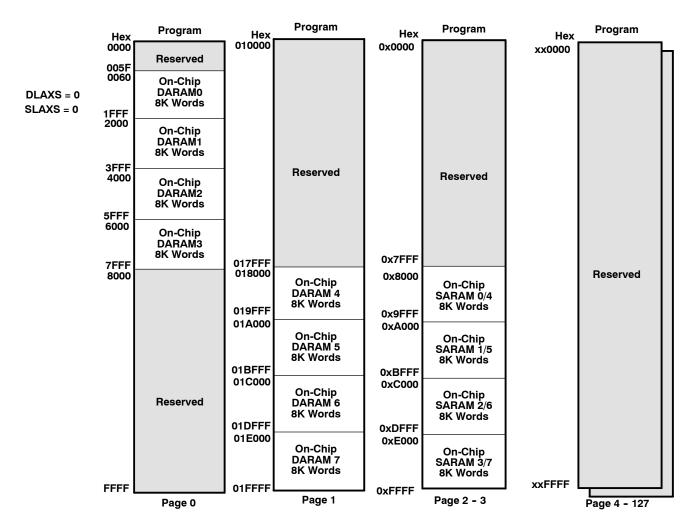

| 3-2. Program and Data Memory Map                                                       | 13   |

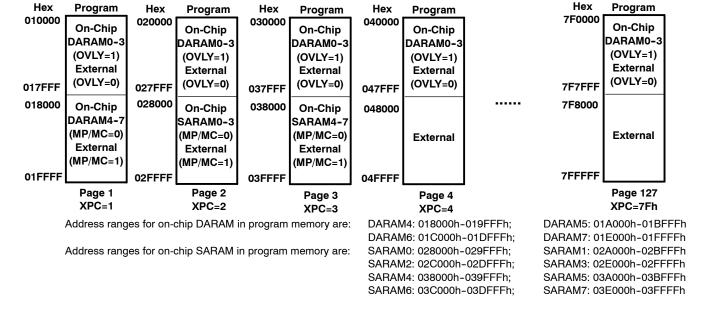

| 3-3. Extended Program Memory Map                                                       | 13   |

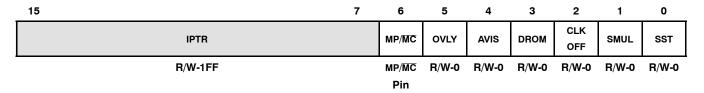

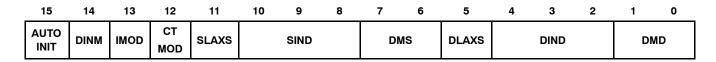

| 3-4. Processor Mode Status (PMST) Register                                             | 14   |

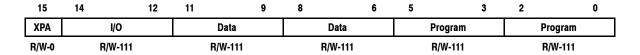

| 3-5. Software Wait-State Register (SWWSR) [Memory-Mapped Register (MMR) Address 0028h] |      |

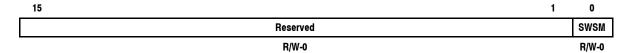

| 3-6. Software Wait-State Control Register (SWCR) [MMR Address 002Bh]                   | 17   |

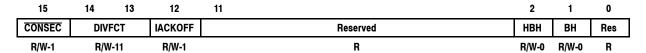

| 3-7. Bank-Switching Control Register (BSCR) [MMR Address 0029h]                        | 17   |

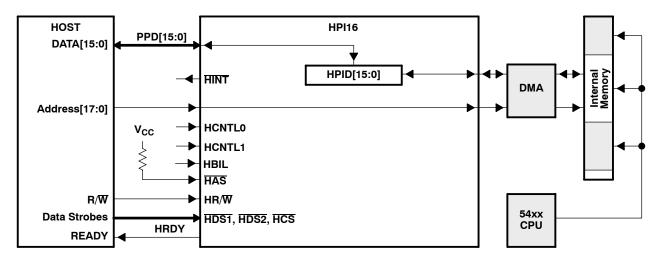

| 3-8. Host-Port Interface — Nonmultiplexed Mode                                         | 20   |

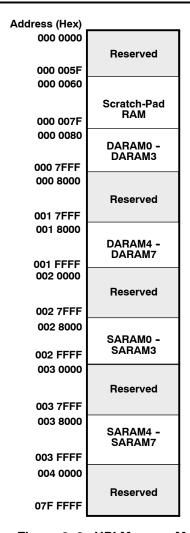

| 3-9. HPI Memory Map                                                                    | 21   |

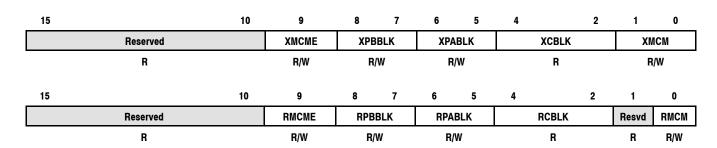

| 3-10. Multichannel Control Registers (MCR1 and MCR2)                                   | 23   |

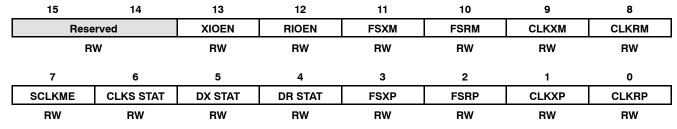

| 3-11. Pin Control Register (PCR)                                                       | 23   |

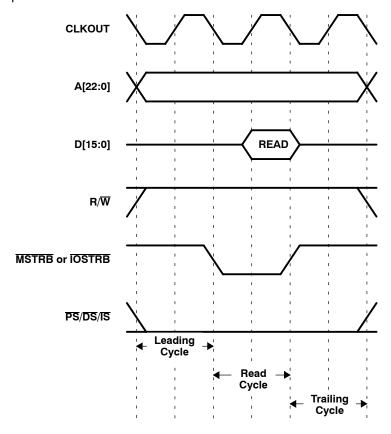

| 3-12. Nonconsecutive Memory Read and I/O Read Bus Sequence                             | 26   |

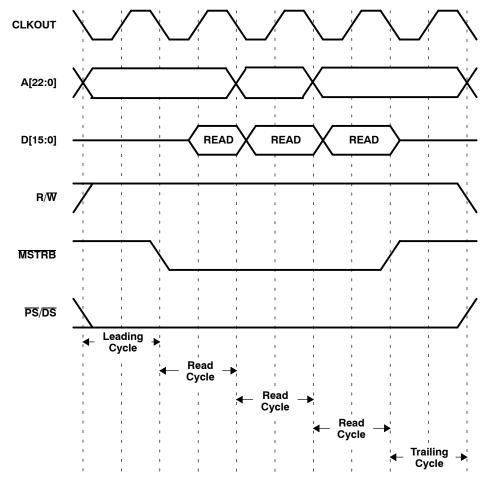

| 3-13. Consecutive Memory Read Bus Sequence (n = 3 reads)                               | 27   |

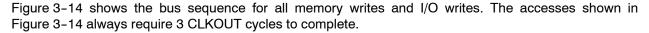

| 3-14. Memory Write and I/O Write Bus Sequence                                          | 28   |

| 3-15. DMA Transfer Mode Control Register (DMMCRn)                                      | 29   |

| 3-16. On-Chip DMA Memory Map for Program Space (DLAXS = 0 and SLAXS = 0)               | 30   |

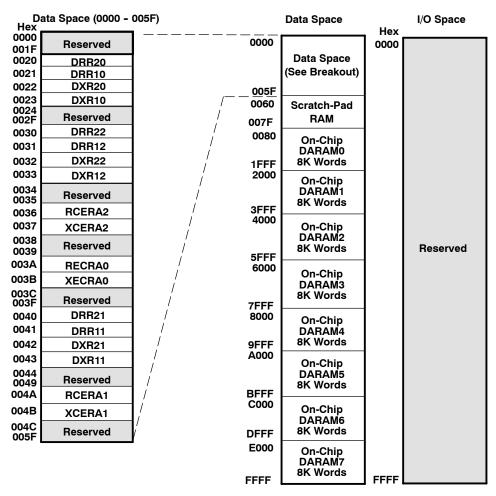

| 3-17. On-Chip DMA Memory Map for Data and IO Space (DLAXS = 0 and SLAXS = 0)           | 31   |

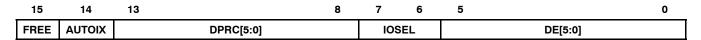

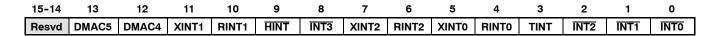

| 3-18. DMPREC Register                                                                  | 32   |

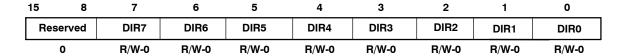

| 3-19. General-Purpose I/O Control Register (GPIOCR) [MMR Address 003Ch]                | 34   |

| 3-20. General-Purpose I/O Status Register (GPIOSR) [MMR Address 003Dh]                 | 34   |

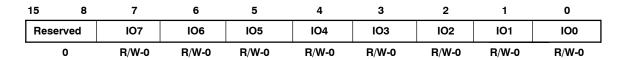

| 3-21. Device ID Register (CSIDR) [MMR Address 003Eh]                                   | 35   |

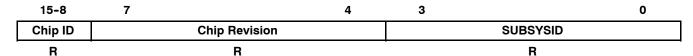

| 3–22. IFR and IMR                                                                      | 41   |

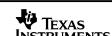

| 5-1. 3.3-V Test Load Circuit                                                           | 44   |

| 5-2. Internal Divide-by-Two Clock Option With External Crystal                         | 46   |

| 5–3. External Divide-by-Two Clock Timing                                               | 47   |

| 5-4. Multiply-by-One Clock Timing                                                      | 48   |

| 5-5. Nonconsecutive Mode Memory Reads                                                  | 50   |

| 5-6. Consecutive Mode Memory Reads                                                     | 51   |

| 5-7. Memory Write (MSTRB = 0)                                                          | 52   |

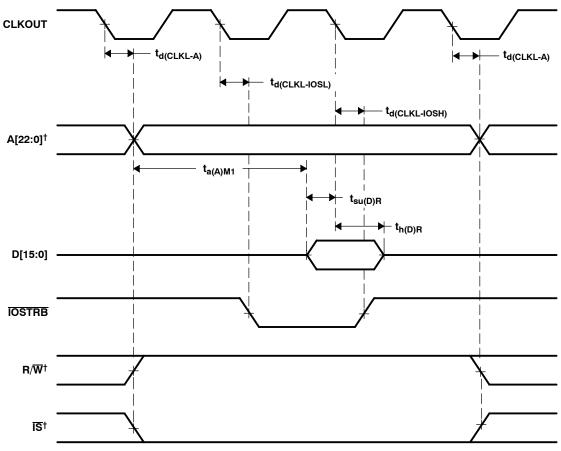

| 5-8. Parallel I/O Port Read (IOSTRB = 0)                                               | 53   |

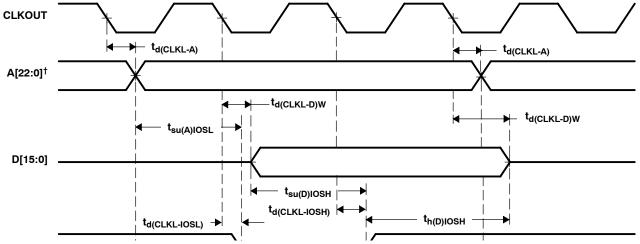

| 5-9. Parallel I/O Port Write (IOSTRB = 0)                                              | 54   |

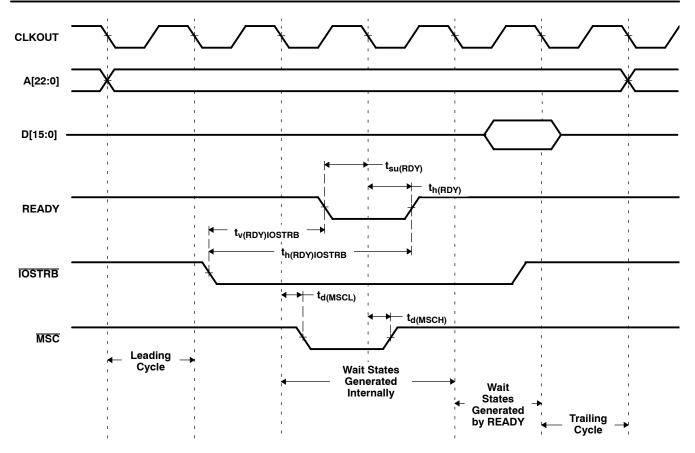

| 5-10. Memory Read With Externally Generated Wait States                                | 56   |

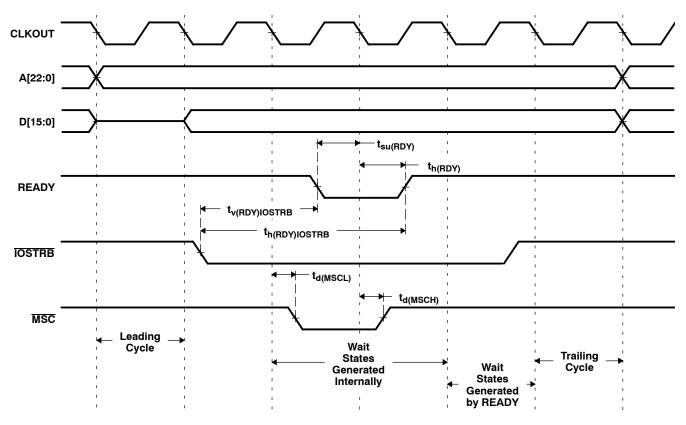

| 5-11. Memory Write With Externally Generated Wait States                               | 57   |

| 5-12. I/O Read With Externally Generated Wait States                                   | 58   |

| 5-13. I/O Write With Externally Generated Wait States                                  | 59   |

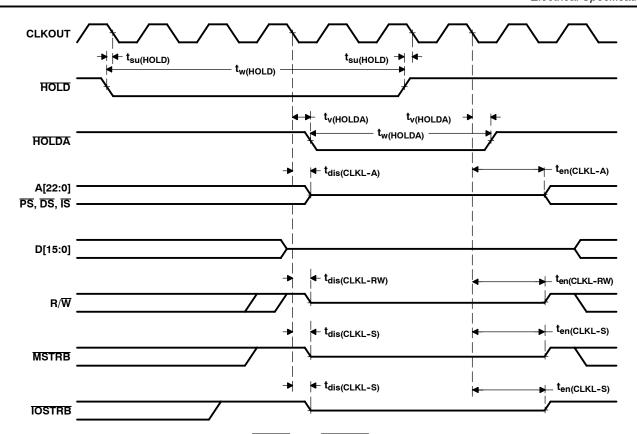

| 5-14. HOLD and HOLDA Timings (HM = 1)                                                  | 61   |

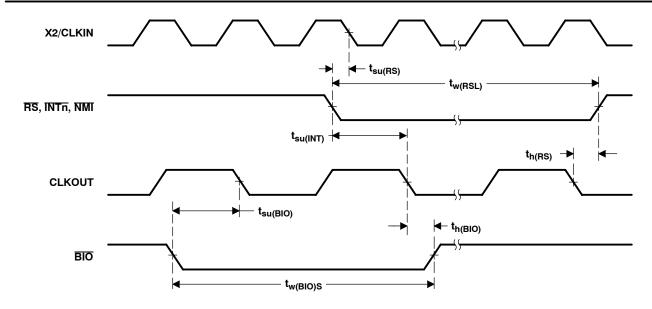

| 5-15. Reset and BIO Timings                                                            |      |

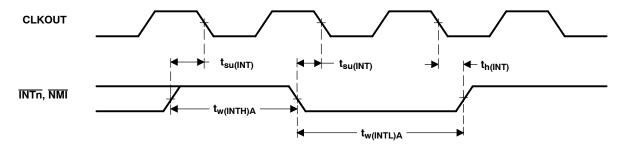

| 5–16. Interrupt Timing                                                                 | 63   |

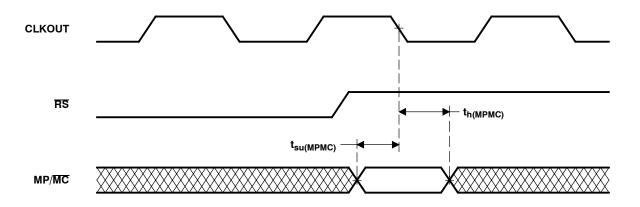

| 5-17. MP/MC Timing                                                                     | 63   |

# Figures

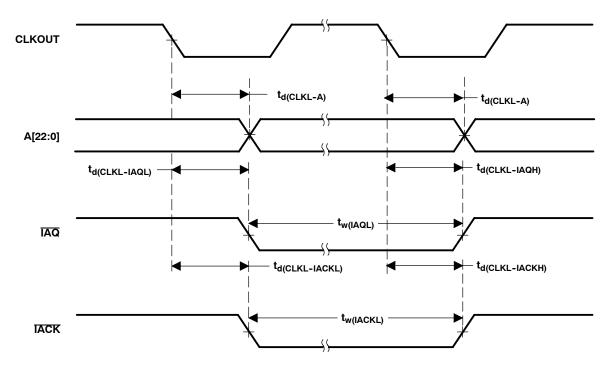

| 5-18. | Instruction Acquisition (IAQ) and Interrupt Acknowledge (IACK) Timings | 64 |

|-------|------------------------------------------------------------------------|----|

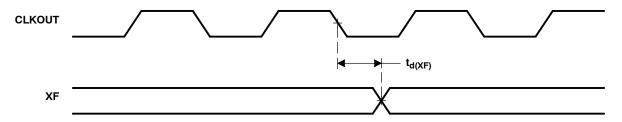

| 5-19. | External Flag (XF) Timing                                              | 65 |

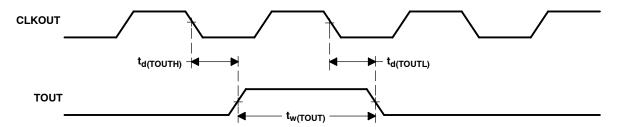

| 5-20. | TOUT Timing                                                            | 65 |

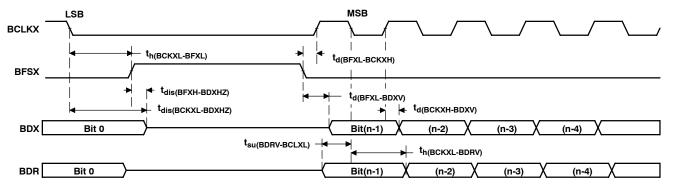

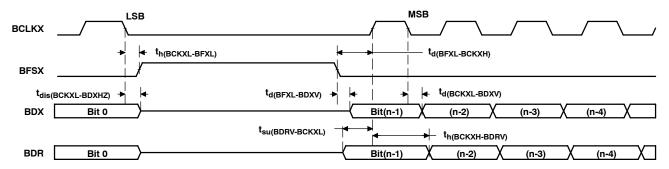

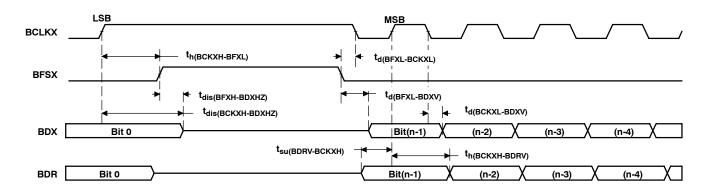

| 5-21. | McBSP Receive Timings                                                  | 67 |

| 5-22. | McBSP Transmit Timings                                                 | 68 |

| 5-23. | McBSP General-Purpose I/O Timings                                      | 69 |

| 5-24. | McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 0           | 70 |

| 5-25. | McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 0           | 71 |

| 5-26. | McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 1           | 72 |

| 5-27. | McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 1           | 73 |

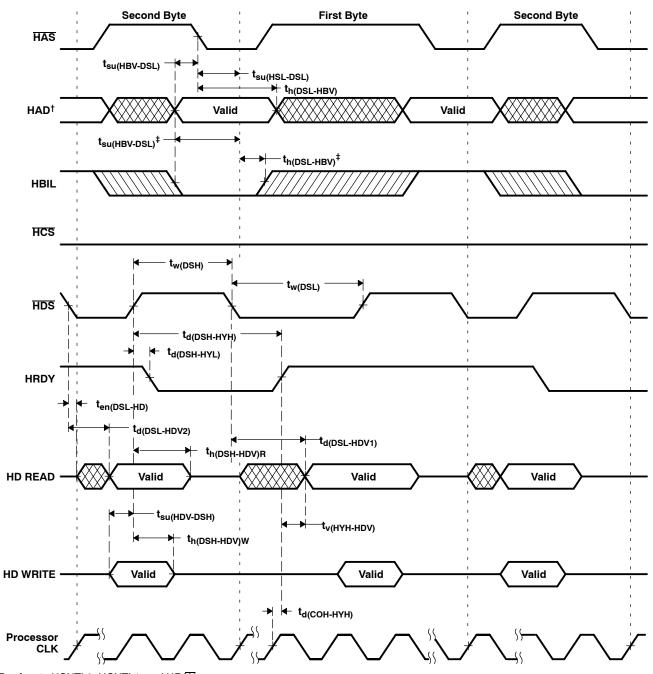

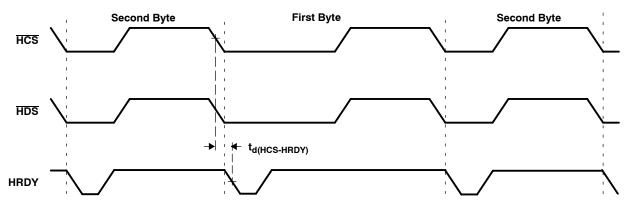

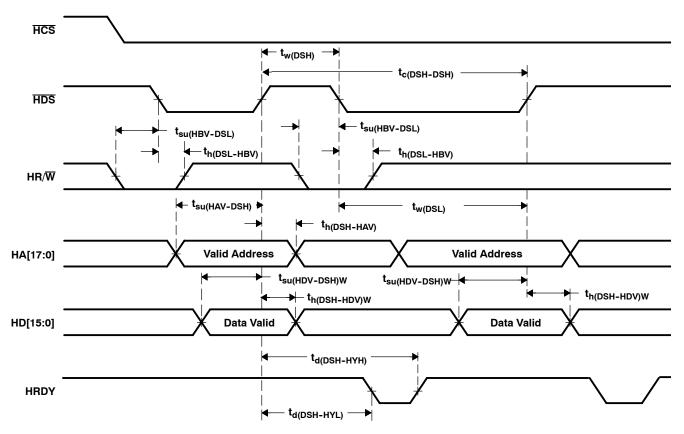

| 5-28. | Using HDS to Control Accesses (HCS Always Low)                         | 76 |

| 5-29. | Using HCS to Control Accesses                                          | 77 |

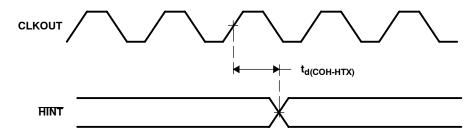

| 5-30. | HINT Timing                                                            | 77 |

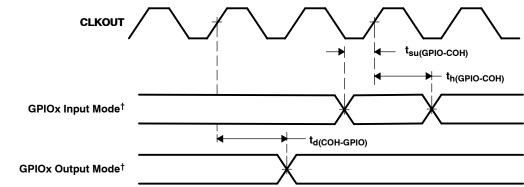

| 5-31. | GPIOx Timings                                                          | 77 |

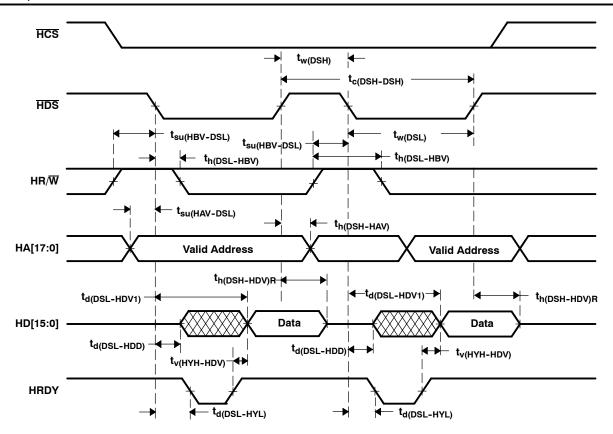

| 5-32. | Nonmultiplexed Read Timings                                            | 80 |

| 5-33. | Nonmultiplexed Write Timings                                           | 81 |

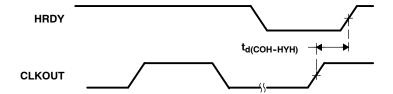

| 5-34. | HRDY Relative to CLKOUT                                                | 81 |

| 6_1 9 | SM I320VC5416 164-Pin Ceramic Quad Flatnack (HEG)                      | 82 |

# **List of Tables**

| Table                                                                                                                                                                    | Page  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 2-1. Terminal Assignments for the SMJ320VC5416HFG (164-Pin CQFP Package)†                                                                                                | 3     |

| 2-2. Signal Descriptions                                                                                                                                                 | 5     |

| 3-1. Standard On-Chip ROM Layout†                                                                                                                                        |       |

| 3-2. Processor Mode Status (PMST) Register Bit Fields                                                                                                                    | 15    |

| 3-3. Software Wait-State Register (SWWSR) Bit Fields                                                                                                                     | 16    |

| 3-4. Software Wait-State Control Register (SWCR) Bit Fields                                                                                                              | 17    |

| 3-5. Bank-Switching Control Register (BSCR) Fields                                                                                                                       | 18    |

| 3-6. Bus Holder Control Bits                                                                                                                                             | 19    |

| 3-7. Sample Rate Input Clock Selection                                                                                                                                   | 23    |

| 3-8. Clock Mode Settings at Reset                                                                                                                                        |       |

| 3-9. DMD Section of the DMMCRn Register                                                                                                                                  |       |

| 3-10. DMA Reload Register Selection                                                                                                                                      |       |

| 3-11. DMA Interrupts                                                                                                                                                     |       |

| 3-12. DMA Synchronization Events                                                                                                                                         |       |

| 3-13. DMA Channel Interrupt Selection                                                                                                                                    |       |

| 3-14. CPU Memory-Mapped Registers                                                                                                                                        |       |

| 3-15. Peripheral Memory-Mapped Registers for Each DSP Subsystem                                                                                                          |       |

| 3-16. McBSP Control Registers and Subaddresses                                                                                                                           |       |

| 3-17. DMA Subbank Addressed Registers                                                                                                                                    |       |

| 3-18. Interrupt Locations and Priorities                                                                                                                                 |       |

| 5-1. Thermal Resistance Characteristics                                                                                                                                  |       |

| 5-2. Input Clock Frequency Characteristics                                                                                                                               |       |

| 5-3. Clock Mode Pin Settings for the Divide-By-2 and By Divide-by-4 Clock Options                                                                                        |       |

| 5-4. Divide-By-2 and Divide-by-4 Clock Options Timing Requirements                                                                                                       |       |

| 5-5. Divide-By-2 and Divide-by-4 Clock Options Switching Characteristics                                                                                                 |       |

| 5-6. Multiply-By-N Clock Option Timing Requirements                                                                                                                      |       |

| 5-7. Multiply-By-N Clock Option Switching Characteristics                                                                                                                |       |

| 5-8. Memory Read Timing Requirements                                                                                                                                     |       |

| 5-9. Memory Read Switching Characteristics                                                                                                                               |       |

| 5-10. Memory Write Switching Characteristics                                                                                                                             |       |

| 5-11. I/O Read Timing Requirements                                                                                                                                       |       |

| 5-12. I/O Read Switching Characteristics                                                                                                                                 |       |

| 5-13. I/O Write Switching Characteristics                                                                                                                                |       |

| 5-14. Ready Timing Requirements for Externally Generated Wait States†                                                                                                    |       |

| 5-15. Ready Switching Characteristics for Externally Generated Wait States†                                                                                              |       |

| 5-16. HOLD and HOLDA Timing Requirements                                                                                                                                 |       |

| 5-17. HOLD and HOLDA Switching Characteristics                                                                                                                           |       |

| 5-18. Reset, BIO, Interrupt, and MP/MC Timing Requirements                                                                                                               |       |

| 5-19. Instruction Acquisition (IAQ) and Interrupt Acknowledge (IACK) Switching Characterist                                                                              |       |

| 5-20. External Flag (XF) and TOUT Switching Characteristics                                                                                                              |       |

| 5-21. McBSP Transmit and Receive Timing Requirements†                                                                                                                    |       |

| 5-22. McBSP Transmit and Receive Switching Characteristics†                                                                                                              |       |

| 5-23. McBSP General-Purpose I/O Timing Requirements                                                                                                                      |       |

| 5-24. McBSP General-Purpose I/O Switching Characteristics                                                                                                                |       |

| 5-25. McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 0)7 5-26. McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 0) |       |

| 5-20. IVICEOF AS OF I IVIASIE! OF STAVE SWITCHING CHARACTERSTICS (OLNOTP = 100, OLNAP = 0)                                                                               | /1 /0 |

## Tables

| 5-27. | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 0)†       | 71 |

|-------|-----------------------------------------------------------------------------------|----|

| 5-28. | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 0)† | 71 |

| 5-29. | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 1)†       | 72 |

| 5-30. | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 1)† | 72 |

| 5-31. | McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 1)†       | 73 |

| 5-32. | McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 1)† | 73 |

| 5-33. | HPI8 Mode Timing Requirements                                                     | 74 |

| 5-34. | HPI8 Mode Switching Characteristics                                               | 75 |

| 5-35. | HPI16 Mode Timing Requirements                                                    | 78 |

| 5-36  | HPI16 Mode Switching Characteristics                                              | 70 |

# 1 SMJ320VC5416 Features

- Processed to MIL-PRF-38535 (QML)

- Advanced Multibus Architecture With Three Separate 16-Bit Data Memory Buses and One Program Memory Bus

- 40-Bit Arithmetic Logic Unit (ALU) Including a 40-Bit Barrel Shifter and Two Independent 40-Bit Accumulators

- 17 x 17-Bit Parallel Multiplier Coupled to a 40-Bit Dedicated Adder for Non-Pipelined Single-Cycle Multiply/Accumulate (MAC) Operation

- Compare, Select, and Store Unit (CSSU) for the Add/Compare Selection of the Viterbi Operator

- Exponent Encoder to Compute an Exponent Value of a 40-Bit Accumulator Value in a Single Cycle

- Two Address Generators With Eight Auxiliary Registers and Two Auxiliary Register Arithmetic Units (ARAUs)

- Data Bus With a Bus Holder Feature

- Extended Addressing Mode for 8M x 16-Bit Maximum Addressable External Program Space

- 128K x 16-Bit On-Chip RAM Composed of:

- Eight Blocks of 8K x 16-Bit On-Chip Dual-Access Program/Data RAM

- Eight Blocks of 8K x 16-Bit On-Chip Single-Access Program RAM

- 16K x 16-Bit On-Chip ROM Configured for Program Memory

- Enhanced External Parallel Interface (XIO2)

- Single-Instruction-Repeat and Block-Repeat Operations for Program Code

- Block-Memory-Move Instructions for Better Program and Data Management

- Instructions With a 32-Bit Long Word Operand

- Instructions With Two- or Three-Operand Reads

- Arithmetic Instructions With Parallel Store and Parallel Load

- Conditional Store Instructions

- Fast Return From Interrupt

- On-Chip Peripherals

- Software-Programmable Wait-State Generator and Programmable Bank-Switching

- On-Chip Programmable Phase-Locked Loop (PLL) Clock Generator With External Clock Source

- One 16-Bit Timer

- Six-Channel Direct Memory Access (DMA) Controller

- Three Multichannel Buffered Serial Ports (McBSPs)

- 8/16-Bit Enhanced Parallel Host-Port Interface (HPI8/16)

- Power Consumption Control With IDLE1, IDLE2, and IDLE3 Instructions With Power-Down Modes

- CLKOUT Off Control to Disable CLKOUT

- On-Chip Scan-Based Emulation Logic, IEEE Std 1149.1<sup>†</sup> (JTAG) Boundary Scan Logic

- 164-Pin Ceramic Quad Flatpack (CQFP) (HFG Suffix)

- 10-ns Single-Cycle Fixed-Point Instruction Execution Time (100 MIPS)

- 3.3-V I/O Supply Voltage

- 1.5-V Core Supply Voltage

- -55°C to 115°C Operating Temperature Range, QML Processing

<sup>†</sup> IEEE Standard 1149.1-1990 Standard-Test-Access Port and Boundary Scan Architecture.

# 2 Introduction

This section describes the main features of the SMJ320VC5416, lists the pin assignments, and describes the function of each pin. This data manual also provides a detailed description section, electrical specifications, parameter measurement information, and mechanical data about the available packaging.

**NOTE:** This data manual is designed to be used in conjunction with the *TMS320C54x*™ *DSP Functional Overview* (literature number SPRU307).

# 2.1 Description

The SMJ320VC5416 fixed-point, digital signal processor (DSP) (hereafter referred to as the 5416 unless otherwise specified) is based on an advanced modified Harvard architecture that has one program memory bus and three data memory buses. This processor provides an arithmetic logic unit (ALU) with a high degree of parallelism, application-specific hardware logic, on-chip memory, and additional on-chip peripherals. The basis of the operational flexibility and speed of this DSP is a highly specialized instruction set.

Separate program and data spaces allow simultaneous access to program instructions and data, providing a high degree of parallelism. Two read operations and one write operation can be performed in a single cycle. Instructions with parallel store and application-specific instructions can fully utilize this architecture. In addition, data can be transferred between data and program spaces. Such parallelism supports a powerful set of arithmetic, logic, and bit-manipulation operations that can all be performed in a single machine cycle. The 5416 also includes the control mechanisms to manage interrupts, repeated operations, and function calls.

# 2.2 Pin Assignments

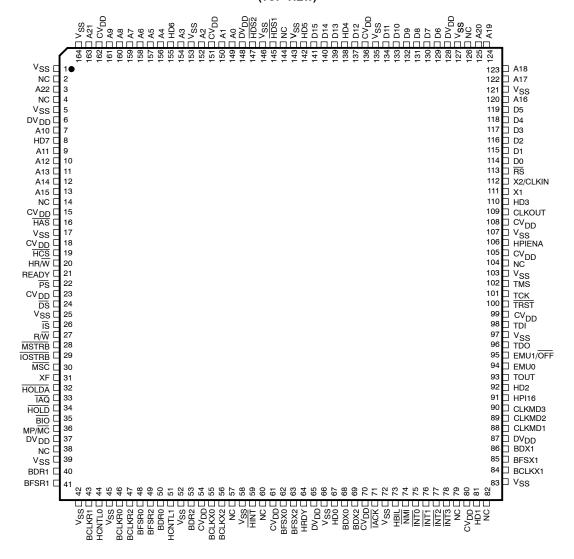

Figure 2-1 provides the pin assignments for the 164-pin ceramic quad flatpack (CQFP) package.

Table 2-2 lists terminal names, terminal functions, and operating modes for the SMJ320VC5416.

Table 2-1. Terminal Assignments for the SMJ320VC5416HFG (164-Pin CQFP Package)<sup>†</sup>

| PIN NUMBER | PIN NAME         |

|------------|------------------|------------|------------------|------------|------------------|------------|------------------|

| 1          | $V_{SS}$         | 42         | $V_{SS}$         | 83         | $V_{SS}$         | 124        | A19              |

| 2          | NC               | 43         | BCLKR1           | 84         | BCLKX1           | 125        | A20              |

| 3          | A22              | 44         | HCNTL0           | 85         | BFSX1            | 126        | NC               |

| 4          | NC               | 45         | V <sub>SS</sub>  | 86         | BDX1             | 127        | V <sub>SS</sub>  |

| 5          | V <sub>SS</sub>  | 46         | BCLKR0           | 87         | DV <sub>DD</sub> | 128        | DV <sub>DD</sub> |

| 6          | DV <sub>DD</sub> | 47         | BCLKR2           | 88         | CLKMD1           | 129        | D6               |

| 7          | A10              | 48         | BFSR0            | 89         | CLKMD2           | 130        | D7               |

| 8          | HD7              | 49         | BFSR2            | 90         | CLKMD3           | 131        | D8               |

| 9          | A11              | 50         | BDR0             | 91         | HPI16            | 132        | D9               |

| 10         | A12              | 51         | HCNTL1           | 92         | HD2              | 133        | D10              |

| 11         | A13              | 52         | V <sub>SS</sub>  | 93         | TOUT             | 134        | D11              |

| 12         | A14              | 53         | BDR2             | 94         | EMU0             | 135        | V <sub>SS</sub>  |

| 13         | A15              | 54         | CV <sub>DD</sub> | 95         | EMU1/OFF         | 136        | CV <sub>DD</sub> |

| 14         | NC               | 55         | BCLKX0           | 96         | TDO              | 137        | D12              |

| 15         | CV <sub>DD</sub> | 56         | BCLKX2           | 97         | V <sub>SS</sub>  | 138        | HD4              |

| 16         | HAS              | 57         | NC               | 98         | TDI              | 139        | D13              |

| 17         | V <sub>SS</sub>  | 58         | V <sub>SS</sub>  | 99         | CV <sub>DD</sub> | 140        | D14              |

| 18         | CV <sub>DD</sub> | 59         | HINT             | 100        | TRST             | 141        | D15              |

| 19         | HCS              | 60         | NC               | 101        | TCK              | 142        | HD5              |

| 20         | HR/₩             | 61         | CV <sub>DD</sub> | 102        | TMS              | 143        | V <sub>SS</sub>  |

| 21         | READY            | 62         | BFSX0            | 103        | V <sub>SS</sub>  | 144        | NC               |

| 22         | PS               | 63         | BFSX2            | 104        | NC               | 145        | HDS1             |

| 23         | CV <sub>DD</sub> | 64         | HRDY             | 105        | CV <sub>DD</sub> | 146        | V <sub>SS</sub>  |

| 24         | DS               | 65         | DV <sub>DD</sub> | 106        | HPIENA           | 147        | HDS2             |

| 25         | V <sub>SS</sub>  | 66         | V <sub>SS</sub>  | 107        | V <sub>SS</sub>  | 148        | DV <sub>DD</sub> |

| 26         | ĪS               | 67         | HD0              | 108        | CV <sub>DD</sub> | 149        | A0               |

| 27         | R/W              | 68         | BDX0             | 109        | CLKOUT           | 150        | A1               |

| 28         | MSTRB            | 69         | BDX2             | 110        | HD3              | 151        | CV <sub>DD</sub> |

| 29         | ĪOSTRB           | 70         | CV <sub>DD</sub> | 111        | X1               | 152        | A2               |

| 30         | MSC              | 71         | ĪACK             | 112        | X2/CLKIN         | 153        | V <sub>SS</sub>  |

| 31         | XF               | 72         | V <sub>SS</sub>  | 113        | RS               | 154        | А3               |

| 32         | HOLDA            | 73         | HBIL             | 114        | D0               | 155        | HD6              |

| 33         | ĪĀQ              | 74         | NMI              | 115        | D1               | 156        | A4               |

| 34         | HOLD             | 75         | ĪNT0             | 116        | D2               | 157        | A5               |

| 35         | BIO              | 76         | ĪNT1             | 117        | D3               | 158        | A6               |

| 36         | MP/MC            | 77         | ĪNT2             | 118        | D4               | 159        | A7               |

| 37         | $DV_DD$          | 78         | ĪNT3             | 119        | D5               | 160        | A8               |

| 38         | NC               | 79         | NC               | 120        | A16              | 161        | A9               |

| 39         | V <sub>SS</sub>  | 80         | CV <sub>DD</sub> | 121        | V <sub>SS</sub>  | 162        | CV <sub>DD</sub> |

| 40         | BDR1             | 81         | HD1              | 122        | A17              | 163        | A21              |

| 41         | BFSR1            | 82         | NC               | 123        | A18              | 164        | V <sub>SS</sub>  |

$<sup>^{\</sup>dagger}$  DV<sub>DD</sub> is the power supply for the I/O pins while CV<sub>DD</sub> is the power supply for the core CPU, and V<sub>SS</sub> is the ground for both the I/O pins and the core CPU.

# 2.2.1 Pin Assignments for the HFG Package

The SMJ320VC5416HFG 164-pin ceramic quad flatpack (CQFP) pin assignments are shown in Figure 2-1.

## HFG PACKAGE†‡ (TOP VIEW)

NC - No internal connection

Figure 2-1. 164-Pin HFG Ceramic Quad Flatpack (Top View)

<sup>†</sup> NC = No connection

<sup>&</sup>lt;sup>‡</sup> DV<sub>DD</sub> is the power supply for the I/O pins while CV<sub>DD</sub> is the power supply for the core CPU, and V<sub>SS</sub> is the ground for both the I/O pins and the core CPU.

#### 2.3 **Signal Descriptions**

Table 2-2 lists each signal, function, and operating mode(s) grouped by function. See Section 2.2 for exact pin locations based on package type.

Table 2-2. Signal Descriptions

|                                                                                                  | Table 2-2. Signal Descriptions |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|--------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TERMINAL I/O†                                                                                    |                                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|                                                                                                  |                                | DATA SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| A22 (MS<br>A21<br>A20<br>A19<br>A18<br>A17                                                       | SB) I/O/Z <sup>‡§</sup>        | Parallel address bus A22 [most significant bit (MSB)] through A0 [least significant bit (LSB)]. The sixteen LSB lines, A0 to A15, are multiplexed to address external memory (program, data) or I/O. The seven MSB lines, A16 to A22, address external program space memory. A22-A0 is placed in the high-impedance state in the hold mode. A22-A0 also goes into the high-impedance state when OFF is low.  A17-A0 are inputs in HPI16 mode. These pins can be used to address internal memory via the host-port interface                                                                                                                                                                                                                          |  |  |

| A16<br>A15                                                                                       |                                | (HPI) when the HPI16 pin is high. These pins also have Schmitt trigger inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| A14<br>A13<br>A12<br>A11<br>A10<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0 (LSI | В)                             | The address bus has a bus holder feature that eliminates passive components and the power dissipation associated with them. The bus holder keeps the address bus at the previous logic level when the bus goes into a high-impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| D15 (MS D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 (LSi                                   |                                | Parallel data bus D15 (MSB) through D0 (LSB). D15–D0 is multiplexed to transfer data between the core CPU and external data/program memory or I/O devices or HPI in HPI16 mode (when HPI16 pin is high). D15–D0 is placed in the high-impedance state when not outputting data or when RS or HOLD is asserted. D15–D0 also goes into the high-impedance state when OFF is low. These pins also have Schmitt trigger inputs.  The data bus has a bus holder feature that eliminates passive components and the power dissipation associated with them. The bus holder keeps the data bus at the previous logic level when the bus goes into the high-impedance state. The bus holders on the data bus can be enabled/disabled under software control. |  |  |

<sup>†</sup> I = Input, O = Output, Z = High-impedance, S = Supply † These pins have Schmitt trigger inputs.

<sup>§</sup> This pin has an internal bus holder controlled by way of the BSCR register.

This pin has an internal pullup resistor.

<sup>#</sup> This pin has an internal pulldown resistor.

Table 2-2. Signal Descriptions (Continued)

| TERMINAL 19t                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| I/O†                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| INITIALIZATION, INTERRUPT AND RESET OPERATIONS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| O/Z                                            | Interrupt acknowledge signal. IACK indicates receipt of an interrupt and that the program counter is fetching the interrupt vector location designated by A15-A0. IACK also goes into the high-impedance state when OFF is low.                                                                                                                                                                                                                                           |  |  |  |

| 1                                              | External user interrupt inputs. INTO-INT3 are maskable and are prioritized by the interrupt mask register (IMR) and the interrupt mode bit. INTO -INT3 can be polled and reset by way of the interrupt flag register (IFR).                                                                                                                                                                                                                                               |  |  |  |

| I                                              | Nonmaskable interrupt. NMI is an external interrupt that cannot be masked by way of the INTM or the IMR. When NMI is activated, the processor traps to the appropriate vector location.                                                                                                                                                                                                                                                                                   |  |  |  |

| 1                                              | Reset. $\overline{\text{RS}}$ causes the digital signal processor (DSP) to terminate execution and forces the program counter to 0FF80h. When $\overline{\text{RS}}$ is brought to a high level, execution begins at location 0FF80h of program memory. $\overline{\text{RS}}$ affects various registers and status bits.                                                                                                                                                 |  |  |  |

| I                                              | Microprocessor/microcomputer mode select. If active low at reset, microcomputer mode is selected, and the internal program ROM is mapped into the upper 16K words of program memory space. If the pin is driven high during reset, microprocessor mode is selected, and the on-chip ROM is removed from program space. This pin is only sampled at reset, and the MP/MC bit of the processor mode status (PMST) register can override the mode that is selected at reset. |  |  |  |

|                                                | MULTIPROCESSING SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 1                                              | Branch control. A branch can be conditionally executed when $\overline{\text{BIO}}$ is active. If low, the processor executes the conditional instruction. The $\overline{\text{BIO}}$ condition is sampled during the decode phase of the pipeline for the XC instruction, and all other instructions sample $\overline{\text{BIO}}$ during the read phase of the pipeline.                                                                                              |  |  |  |

| O/Z                                            | External flag output (latched software-programmable signal). XF is set high by the SSBX XF instruction, set low by RSBX XF instruction or by loading ST1. XF is used for signaling other processors in multiprocessor configurations or used as a general-purpose output pin. XF goes into the high-impedance state when OFF is low, and is set high at reset.                                                                                                            |  |  |  |

|                                                | MEMORY CONTROL SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| O/Z                                            | Data, program, and I/O space select signals. DS, PS, and TS are always high unless driven low for communicating to a particular external space. Active period corresponds to valid address information. DS, PS, and TS are placed into the high-impedance state in the hold mode; these signals also go into the high-impedance state when OFF is low.                                                                                                                    |  |  |  |

| O/Z                                            | Memory strobe signal. MSTRB is always high unless low-level asserted to indicate an external bus access to data or program memory. MSTRB is placed in the high-impedance state in the hold mode; it also goes into the high-impedance state when OFF is low.                                                                                                                                                                                                              |  |  |  |

| I                                              | Data ready. READY indicates that an external device is prepared for a bus transaction to be completed. If the device is not ready (READY is low), the processor waits one cycle and checks READY again. Note that the processor performs ready detection if at least two software wait states are programmed. The READY signal is not sampled until the completion of the software wait states.                                                                           |  |  |  |

| O/Z                                            | Read/write signal. $R/\overline{W}$ indicates transfer direction during communication to an external device. $R/\overline{W}$ is normally in the read mode (high), unless it is asserted low when the DSP performs a write operation. $R/\overline{W}$ is placed in the high-impedance state in the hold mode; and it also goes into the high-impedance state when $\overline{OFF}$ is low.                                                                               |  |  |  |

| O/Z                                            | I/O strobe signal. $\overline{\text{IOSTRB}}$ is always high unless low-level asserted to indicate an external bus access to an I/O device. $\overline{\text{IOSTRB}}$ is placed in the high-impedance state in the hold mode; it also goes into the high-impedance state when $\overline{\text{OFF}}$ is low.                                                                                                                                                            |  |  |  |

| I                                              | Hold input. HOLD is asserted to request control of the address, data, and control lines. When acknowledged by the 5416, these lines go into the high-impedance state.                                                                                                                                                                                                                                                                                                     |  |  |  |

|                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

<sup>†</sup> I = Input, O = Output, Z = High-impedance, S = Supply

† These pins have Schmitt trigger inputs.

§ This pin has an internal bus holder controlled by way of the BSCR register.

† This pin has an internal pullup resistor.

# This pin has an internal pulldown resistor.

Table 2-2. Signal Descriptions (Continued)

| TERMINAL I/O†                                                     |                                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|-------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                   | MEMORY CONTROL SIGNALS (CONTINUED) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| HOLDA                                                             | O/Z                                | Hold acknowledge. HOLDA indicates to the external circuitry that the processor is in a hold state and that the address, data, and control lines are in the high-impedance state, allowing them to be available to the external circuitry. HOLDA also goes into the high-impedance state when OFF is low. This pin is driven high during reset.                                                                                                                                                                                                                         |  |  |  |  |

| MSC                                                               | O/Z                                | Microstate complete. $\overline{\text{MSC}}$ indicates completion of all software wait states. When two or more software wait states are enabled, the $\overline{\text{MSC}}$ pin goes active at the beginning of the first software wait state and goes inactive high at the beginning of the last software wait state. If connected to the READY input, $\overline{\text{MSC}}$ forces one external wait state after the last internal wait state is completed. $\overline{\text{MSC}}$ also goes into the high-impedance state when $\overline{\text{OFF}}$ is low. |  |  |  |  |

| IAQ                                                               | O/Z                                | Instruction acquisition signal. $\overline{\text{IAQ}}$ is asserted (active low) when there is an instruction address on the address bus and goes into the high-impedance state when $\overline{\text{OFF}}$ is low.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                                                   |                                    | TIMER SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| CLKOUT                                                            | O/Z                                | Clock output signal. CLKOUT can represent the machine-cycle rate of the CPU divided by 1, 2, 3, or 4 as configured in the bank-switching control register (BSCR). Following reset, CLKOUT represents the machine-cycle rate divided by 4.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| CLKMD1 <sup>‡</sup><br>CLKMD2 <sup>‡</sup><br>CLKMD3 <sup>‡</sup> | 1                                  | Clock mode select signals. CLKMD1-CLKMD3 allow the selection and configuration of different clock modes such as crystal, external clock, and PLL mode. The external CLKMD1-CLKMD3 pins are sampled to determine the desired clock generation mode while $\overline{\text{RS}}$ is low. Following reset, the clock generation mode can be reconfigured by writing to the internal clock mode register in software.                                                                                                                                                      |  |  |  |  |

| X2/CLKIN <sup>‡</sup>                                             | I                                  | Clock/oscillator input. If the internal oscillator is not being used, X2/CLKIN functions as the clock input. (This is revision-dependent, see Section 3.10 for additional information.)                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| X1                                                                | 0                                  | Output pin from the internal oscillator for the crystal. If the internal oscillator is not used, X1 should be left unconnected. X1 does not go into the high-impedance state when $\overline{\text{OFF}}$ is low. (This is revision-dependent, see Section 3.10 for additional information.)                                                                                                                                                                                                                                                                           |  |  |  |  |

| тоит                                                              | O/Z                                | Timer output. TOUT signals a pulse when the on-chip timer counts down past zero. The pulse is one CLKOUT cycle wide. TOUT also goes into the high-impedance state when $\overline{\text{OFF}}$ is low.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| MULTICHA                                                          | ANNEL BUF                          | FERED SERIAL PORT 0 (McBSP #0), MULTICHANNEL BUFFERED SERIAL PORT 1 (McBSP #1),<br>AND MULTICHANNEL BUFFERED SERIAL PORT 2 (McBSP #2) SIGNALS                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| BCLKR0 <sup>‡</sup><br>BCLKR1 <sup>‡</sup><br>BCLKR2 <sup>‡</sup> | I/O/Z                              | Receive clock input. BCLKR can be configured as an input or an output; it is configured as an input following reset. BCLKR serves as the serial shift clock for the buffered serial port receiver.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| BDR0<br>BDR1<br>BDR2                                              | I                                  | Serial data receive input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| BFSR0<br>BFSR1<br>BFSR2                                           | I/O/Z                              | Frame synchronization pulse for receive input. BFSR can be configured as an input or an output; it is configured as an input following reset. The BFSR pulse initiates the receive data process over BDR.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| BCLKX0 <sup>‡</sup><br>BCLKX1 <sup>‡</sup><br>BCLKX2 <sup>‡</sup> | I/O/Z                              | Transmit clock. BCLKX serves as the serial shift clock for the McBSP transmitter. BCLKX can be configured as an input or an output, and is configured as an input following reset. BCLKX enters the high-impedance state when OFF goes low.                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| BDX0<br>BDX1<br>BDX2                                              | O/Z                                | Serial data transmit output. BDX is placed in the high-impedance state when not transmitting, when RS is asserted, or when OFF is low.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| BFSX0<br>BFSX1<br>BFSX2                                           | I/O/Z                              | Frame synchronization pulse for transmit input/output. The BFSX pulse initiates the data transmit process over BDX. BFSX can be configured as an input or an output, and is configured as an input following reset. BFSX goes into the high-impedance state when $\overline{\text{OFF}}$ is low.                                                                                                                                                                                                                                                                       |  |  |  |  |

<sup>†</sup> I = Input, O = Output, Z = High-impedance, S = Supply † These pins have Schmitt trigger inputs. § This pin has an internal bus holder controlled by way of the BSCR register.

<sup>¶</sup> This pin has an internal pullup resistor.

# This pin has an internal pulldown resistor.

Table 2-2. Signal Descriptions (Continued)

| TERMINAL<br>NAME                           | I/O†  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|--------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| HOST-PORT INTERFACE SIGNALS                |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| HD0-HD7 <sup>‡§</sup>                      | I/O/Z | Parallel bidirectional data bus. The HPI data bus is used by a host device bus to exchange information with the HPI registers. These pins can also be used as general-purpose I/O pins. HD0-HD7 is placed in the high-impedance state when not outputting data or when OFF is low. The HPI data bus includes bus holders to reduce the static power dissipation caused by floating, unused pins. When the HPI data bus is not being driven by the 5416, the bus holders keep the pins at the previous logic level. The HPI data bus holders are disabled at reset and can be enabled/disabled via the HBH bit of the BSCR. These pins also have Schmitt trigger inputs. |  |  |  |

| HCNTL0 <sup>¶</sup><br>HCNTL1 <sup>¶</sup> | I     | Control inputs. HCNTL0 and HCNTL1 select a host access to one of the three HPI registers. The control inputs have internal pullups that are only enabled when HPIENA = 0. These pins are not used when HPI16 = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| HBIL¶                                      | I     | Byte identification. HBIL identifies the first or second byte of transfer. The HPIL input has an internal pullup resistor that is only enabled when HPIENA = 0. This pin is not used when HPI16 = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| HCS <sup>‡¶</sup>                          | I     | Chip select. HCS is the select input for the HPI and must be driven low during accesses. The chip select input has an internal pullup resistor that is only enabled when HPIENA = 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| HDS1 <sup>‡¶</sup><br>HDS2 <sup>‡¶</sup>   | I     | Data strobe. HDS1 and HDS2 are driven by the host read and write strobes to control the transfer. The strobe inputs have internal pullup resistors that are only enabled when HPIENA = 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| HAS <sup>‡¶</sup>                          | I     | Address strobe. Host with multiplexed address and data pins requires HAS to latch the address in the HPIA register. HAS input has an internal pullup resistor that is only enabled when HPIENA = 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| HR/W <sup>¶</sup>                          | I     | Read/write. $HR/\overline{W}$ controls the direction of the HPI transfer. $HR/\overline{W}$ has an internal pullup resistor that is only enabled when $HPIENA = 0$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| HRDY                                       | O/Z   | Ready output. HRDY goes into the high-impedance state when OFF is low. The ready output informs the host when the HPI is ready for the next transfer. This pin is driven high during reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| HINT                                       | O/Z   | Interrupt output. This output is used to interrupt the host. When the DSP is in reset, $\overline{\text{HINT}}$ is driven high. $\overline{\text{HINT}}$ goes into the high-impedance state when $\overline{\text{OFF}}$ is low. This pin is not used when HPI16 = 1.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| HPIENA#                                    | I     | HPI module select. HPIENA must be tied to $DV_{DD}$ to have HPI selected. If HPIENA is left open or connected to ground, the HPI module is not selected, internal pullup for the HPI input pins are enabled, and the HPI data bus has holders set. HPIENA is provided with an internal pulldown resistor that is always active. HPIENA is sampled when $\overline{\text{RS}}$ goes high and is ignored until $\overline{\text{RS}}$ goes low again. This pin should never be changed while reset is high                                                                                                                                                                |  |  |  |

| HPI16#                                     | I     | HPI16 mode selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |