# —48 V Hot Swap Controller and Digital Power Monitor with PMBus Interface

Data Sheet ADM1075

#### **FEATURES**

Constant power foldback for FET SOA protection

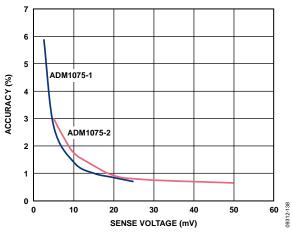

Precision (<1.0%) current and voltage measurement

Controls inrush and faults for negative supply voltages

Suitable for wide input range due to internal shunt regulator

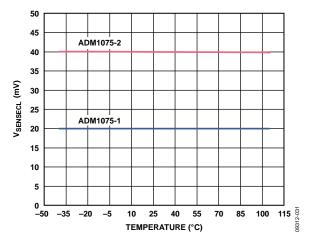

25 mV/50 mV full-scale sense voltage

Fine tune current limit to allow use of standard sense resistor

Soft start inrush current limit profiling

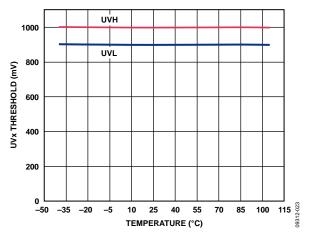

1% accurate UVH and OV pins, 1.5% accurate UVL pin

PMBus/I<sup>2</sup>C interface for control, telemetry, and fault

recording

28-lead LFCSP and TSSOP

-40°C to 105°C junction temperature (T<sub>J</sub>) operating range

#### **APPLICATIONS**

Telecommunication and data communication equipment

Central office switching

-48 V distributed power systems

Negative power supply control

High availability servers

#### **PRODUCT HIGHLIGHTS**

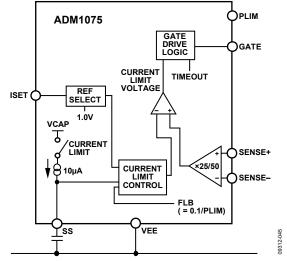

- Constant Power Foldback.

Maximum FET power set by a PLIM resistor divider. This eases complexity when designing to maintain FET SOA.

- 2. Adjustable Current Limit.

The current limit is adjustable via the ISET pin allowing for the use of a standard value sense resistor.

- 12-Bit ADC.

Accurate voltage, current, and power measurements. Also enables calculation of energy consumption over time.

- PMBus/I<sup>2</sup>C Interface.

PMBus fast mode compliant interface used to read back status and data registers and set warning and fault limits.

- Fault Recording.

Latched status registers provide useful debugging information to help trace faults in high reliability systems.

- Built-In Soft Start.

Soft start capacitor controls inrush current profile with di/dt control.

#### **FUNCTIONAL BLOCK DIAGRAM** -48V RTN (0V) 12V RDROP SPLYGD SHDN RESTART 5V VIN 3.3V VCC AND LATCH POWER - 2 8V REFERENCE GPO1/ALERT1/CONV ACCUMULATOR GENERATOR DC-TO-DC ...etc. GPO2/ALERT2 DIGITAL CONVERTER UVH $C_{LOAD}$ SDAO - GND AND PMBUS JNDERVOLTAGE SDAI MULTIPLIER UVL AND SCL OVERVOLTAGE 12-BIT ADC う ADR DETECTOR ADC\_AUX ADC\_V PWRGD FET POWER FOLDBACK DRAIN CONTROL PLIM VCAF SDA ISO FAULT TIMER ADuM1250 **⇔** vee SCL ISO ISE1 N-FET GATE GATE CONTROL CURRENT LIMIT R<sub>SENSE</sub> SENSE VEE G VFF TIMER SS Figure 1.

Rev. B

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

# ADM1075

# **TABLE OF CONTENTS**

| Features 1                                   | Hot Swap Control Commands 3                       | 31 |

|----------------------------------------------|---------------------------------------------------|----|

| Applications1                                | ADM1075 Information Commands 3                    | 31 |

| Product Highlights1                          | Status Commands                                   | 31 |

| Functional Block Diagram1                    | GPO and Alert Pin Setup Commands3                 | 32 |

| Revision History3                            | Power Monitor Commands 3                          | 32 |

| General Description4                         | Warning Limit Setup Commands3                     | 33 |

| Specifications5                              | PMBus Direct Format Conversion3                   | 34 |

| Serial Bus Timing9                           | Voltage and Current Conversion Using LSB Values 3 | 35 |

| Absolute Maximum Ratings10                   | ADM1075 Alert Pin Behavior3                       | 36 |

| Thermal Resistance                           | Faults and Warnings3                              | 36 |

| ESD Caution                                  | Generating an Alert3                              | 36 |

| Pin Configuration and Function Description11 | Handling/Clearing an Alert3                       | 36 |

| Typical Performance Characteristic           | SMBus Alert Response Address                      | 37 |

| Theory of Operation20                        | Example Use of SMBus Alert Response Address 3     | 37 |

| Powering the ADM107520                       | Digital Comparator Mode3                          | 37 |

| Current Sense Inputs                         | PMBus Command Reference                           | 38 |

| Current Limit Reference                      | Register Details3                                 | 39 |

| Setting the Current Limit (ISET)22           | Operation Command Register 3                      | 39 |

| Soft Start                                   | Clear Faults Register3                            | 39 |

| Constant Power Foldback (PLIM)22             | PMBus Capability Register3                        | 39 |

| TIMER                                        |                                                   |    |

| Hot Swap Fault Retry24                       | VIN OV Warn Limit Register3                       | 39 |

| Fast Response to Severe Overcurrent          | VIN UV Warn Limit Register3                       | 39 |

| UV and OV                                    | -                                                 |    |

| PWRGD25                                      | Status Byte Register4                             | 40 |

| DRAIN                                        | Status Word Register4                             | 40 |

| SPLYGD25                                     | IOUT Status Register4                             | 41 |

| LATCH25                                      | Input Status Register4                            | 41 |

| <u>SHDN</u> 25                               |                                                   | 42 |

| RESTART 25                                   | D. LEDVE C.                                       | 43 |

| FET Health                                   | Dood VIN Desistan                                 | 43 |

| Power Monitor                                | Pood IOUT Posistan                                | 43 |

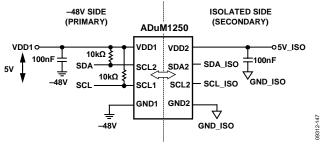

| Isolation                                    | Read PIN Register                                 | 43 |

| PMBus Interface 28                           | DMRue Davision Degister                           | 43 |

| Device Addressing 28                         | Manufacturing ID Pagistar                         | 44 |

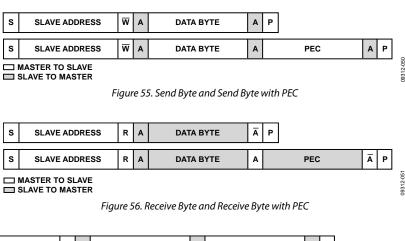

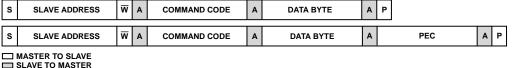

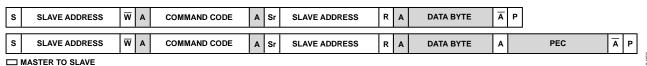

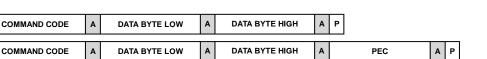

| SMBus Protocol Usage 28                      | Manufacturing Model Pegister                      | 44 |

| Packet Error Checking                        | Manufacturing Payision Pagistar                   | 44 |

| Partial Transactions on I <sup>2</sup> C Bus | Peak IOUT Pagister                                | 44 |

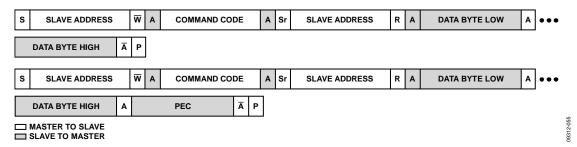

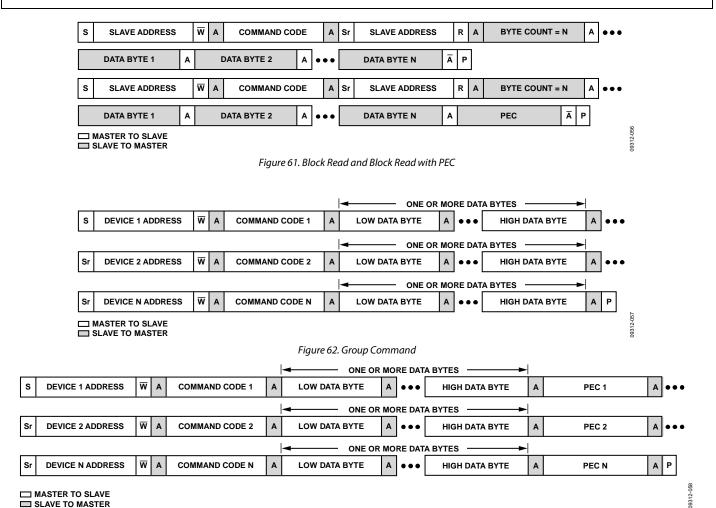

| SMBus Message Formats                        | Peak VIN Register                                 | 45 |

| Group Commands                               | Dools WALLY Degister                              | 45 |

| Group Communication 30                       |                                                   |    |

| Power Monitor Control Register45                                                           | Read PIN_EXT Register                                                                                   | 49 |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----|

| Power Monitor Configuration Register45                                                     | Read EIN_EXT Register                                                                                   | 49 |

| ALERT1 Configuration Register46                                                            | Read VAUX Register                                                                                      | 50 |

| ALERT2 Configuration Register47                                                            | VAUX OV Warn Limit Register                                                                             | 50 |

| IOUT WARN2 Limit Register48                                                                | VAUX UV Warn Limit Register                                                                             | 50 |

| Device Configuration Register48                                                            | VAUX Status Register                                                                                    | 50 |

| Power Cycle Register49                                                                     | Outline Dimensions                                                                                      | 51 |

| Peak PIN Register49                                                                        | Ordering Guide                                                                                          | 51 |

| REVISION HISTORY  4/13—Rev. A to Rev. B  Changes to Figure 4                               | Added Figure 4; Renumbered Sequentially; and changes Table 5 Changes to Current Limit Reference Section | 11 |

| Changes to Figure 43                                                                       | Changes to Voltage and Current Conversion Using LSB Values Section                                      | 35 |

| Change to Bits[1:0], Table 36                                                              | Changes to Table 20 Changes to Table 25 through Table 27                                                |    |

| 3/12—Rev. 0 to Rev. A                                                                      | Changes to Table 23 through Table 27                                                                    |    |

| Added 28-Lead LFCSP Universal Changes to Features Section and Product Highlights Section 1 | Changes to Table 38 and Table 39Changes to Outline Dimensions and Ordering Guide                        | 49 |

| Changes to Table 4                                                                         | 10/11—Revision 0: Initial Version                                                                       |    |

### **GENERAL DESCRIPTION**

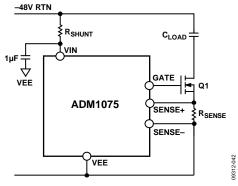

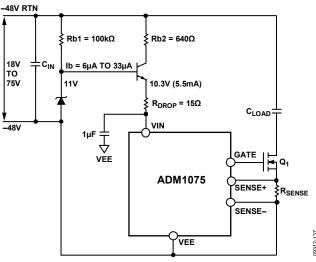

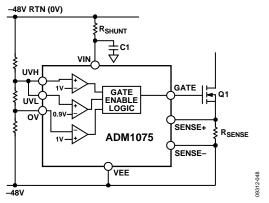

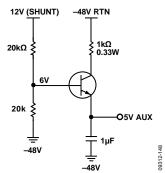

The ADM1075 is a full feature, negative voltage, hot swap controller with constant power foldback and high accuracy digital current and voltage measurement that allows boards to be safely inserted and removed from a live  $-48~\rm V$  backplane. The part provides precise and robust current limiting and protection against both transient and nontransient short circuits and overvoltage and undervoltage conditions. The ADM1075 typically operates from a negative voltage of  $-35~\rm V$  to  $-80~\rm V$  and, due to shunt regulation, has excellent voltage transient immunity. The operating range of the part is flexible due to the shunt regulator, and the part can be powered directly by a  $10~\rm V$  rail to save shunt power dissipation (see the Powering the ADM1075 section for more details).

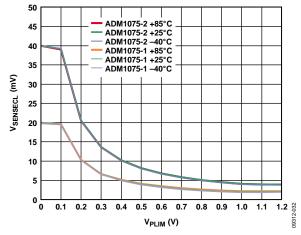

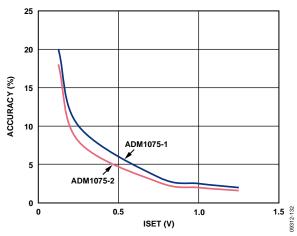

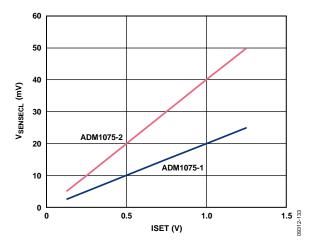

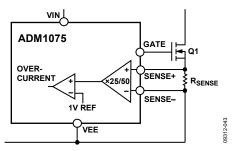

A full-scale current limit of 25 mV or 50 mV can be selected by choosing the appropriate model. The maximum current limit is set by the combination of the sense resistor,  $R_{\text{SENSE}}$ , and the input voltage on the ISET pin, using external resistors. This allows fine tuning of the trip voltage so that standard sense resistors can be used. Inrush current is limited to this programmable value by controlling the gate drive of an external N-channel FET. A built-in soft start function allows control of the inrush current profile by an external capacitor on the soft start (SS) pin.

An external capacitor on the TIMER pin determines the maximum allowed on-time for when the system is in current limit. This is based on the safe operating area (SOA) limits of the MOSFET. A constant power foldback scheme is used to control the power dissipation in the MOSFET during power-up and fault conditions. The ADM1075 regulates the current dynamically to ensure that the power in the MOSFET is within SOA limits as  $V_{DS}$  changes. After the timer has expired, the device shuts down the MOSFET. The level of this power, along with the TIMER regulation time, can be set to ensure that the MOSFET remains within the SOA limits.

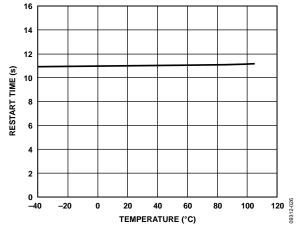

The ADM1075 employs a limited consecutive retry scheme when the LATCH pin is tied to the SHDN pin. In this mode, if the load current reaches the limit, the FET gate is pulled low after the timer expires and retries after a cooling period for seven attempts only. If the fault remains, the device latches off, and the MOSFET is disabled until a manual restart is initiated. Alternatively, the ADM1075 can be set to retry only once by isolating the LATCH pin from the SHDN pin. The part can also be configured to retry an infinite number of times with a 10 second interval between restarts by connecting the GPO2 pin to the RESTART pin.

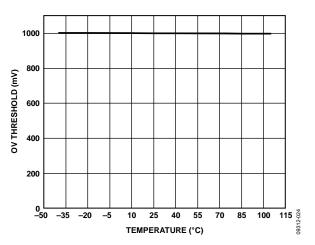

The ADM1075 has separate UVx and OV pins for undervoltage and overvoltage detection. The FET is turned off if a nontransient voltage less than the undervoltage threshold (typically –35 V) is detected on the UVx pins or if greater than the overvoltage threshold (typically –80 V) is detected on the OV pin. The operating voltage range of the ADM1075 is programmable via resistor networks on the UVx and OV pins. The hysteresis levels on the overvoltage detectors can also be altered by selecting the appropriate resistors. There are two separate UVx pins to allow accurate programming of hysteresis.

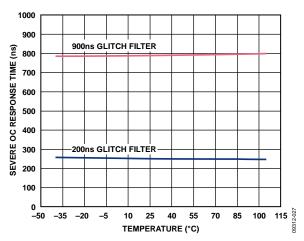

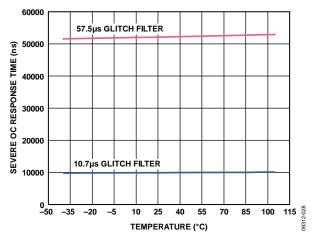

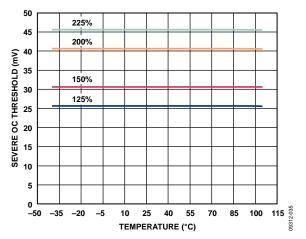

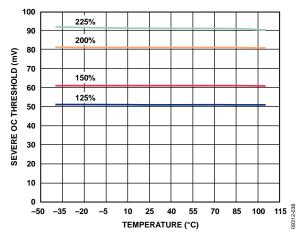

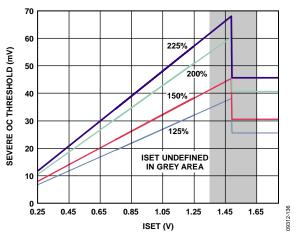

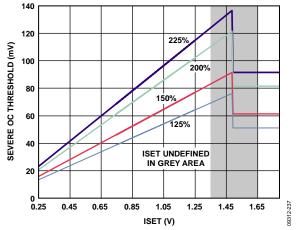

In the case of a short circuit, the ADM1075 has a fast response circuit to detect and respond adequately to this event. If the sense voltage exceeds 1.5 times the normal current limit, a high current (750 mA minimum) gate pull-down switch is activated to shut down the MOSFET as quickly as possible. There is a default internal glitch filter of 900 ns. If a longer filter time or different severe overcurrent limit is required, these parameters can be adjusted via the PMBus<sup>™</sup> interface.

The ADM1075 also includes a 12-bit ADC to provide digital measurement of the voltage and load current. The current is measured at the output of the internal current sense amplifier and the voltage from the ADC\_V input. This data can be read across the PMBus interface.

The PMBus interface allows a controller to read current, voltage, and power measurements from the ADC. Measurements can be initiated by a PMBus command or can be set up to run continuously. The user can read the latest conversion data whenever it is required. A power accumulator is also provided to report total power consumed in a user specified period (total energy). Up to four unique I<sup>2</sup>C addresses can be created, depending on the configuration of the ADR pin.

The GPO1/ALERT1/CONV and GPO2/ALERT2 outputs can be used as a flag to warn a microcontroller or FPGA of one or more fault/warning conditions becoming active. The fault type and level is programmed across the PMBus, and the user can select which faults/warnings activate the alert.

#### Other functions include

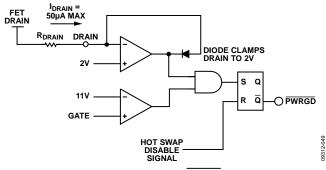

- PWRGD output, which can be used to enable a power module (the DRAIN and GATE pins are monitored to determine when the load capacitance is fully charged)

- SHDN input to manually disable the GATE drive

- RESTART input to remotely initiate a 10 second shutdown

# **SPECIFICATIONS**

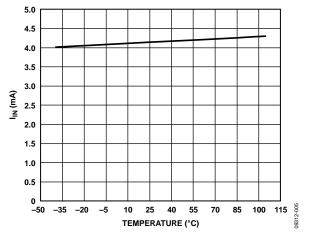

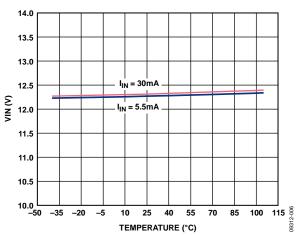

$VEE = -48 \text{ V}, V_{SENSE} = (V_{SENSE+} - V_{SENSE-}) = 0 \text{ mV}, \text{ shunt regulation current} = 10 \text{ mA}, T_J = -40 ^{\circ}\text{C to} + 105 ^{\circ}\text{C}, \text{ unless otherwise noted}.$

Table 1.

| Parameter                                                             | Min        | Тур   | Max   | Unit     | Test Conditions/Comments                                                                                                                                  |

|-----------------------------------------------------------------------|------------|-------|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSTEM SUPPLY                                                         |            |       |       |          |                                                                                                                                                           |

| Voltage Transient Immunity                                            |            | -200  |       | V        |                                                                                                                                                           |

| Typical Operating Voltage                                             | -80        |       | -35   | V        | Determined by external component, R <sub>SHUNT</sub>                                                                                                      |

| SHUNT REGULATOR                                                       |            |       |       |          |                                                                                                                                                           |

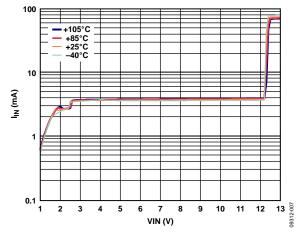

| Operating Supply Voltage Range, VIN                                   | 11.5       | 12.3  | 13    | V        | Shunt regulation voltage, $I_{IN} = 5.5$ mA to 30 mA, maximum $I_{IN}$ dependent on $T_A$ , $\theta_{JA}$ (see the Powering the ADM1075 section)          |

| Quiescent Supply Current                                              |            |       | 5.5   | mA       | VIN = 13 V                                                                                                                                                |

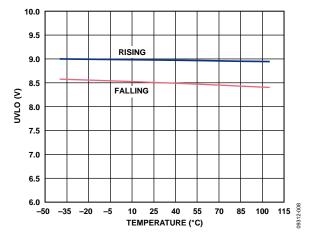

| Undervoltage Lockout, V <sub>UVLO_RISING</sub>                        |            |       | 9.2   | V        |                                                                                                                                                           |

| Undervoltage Lockout Hysteresis                                       |            |       | 600   | mV       |                                                                                                                                                           |

| Power Directly Without Shunt                                          | 9.2        |       | 11.5  | V        |                                                                                                                                                           |

| UV PINS—UNDERVOLTAGE DETECTION                                        |            |       |       |          |                                                                                                                                                           |

| Undervoltage Rising Threshold, V <sub>∪VH</sub>                       | 0.99       | 1.0   | 1.01  | V        |                                                                                                                                                           |

| Undervoltage Falling Threshold, V <sub>UVL</sub>                      | 0.887      | 0.9   | 0.913 | V        |                                                                                                                                                           |

| Total Undervoltage Hysteresis                                         |            | 100   |       | mV       | When UVL and UVH are tied together                                                                                                                        |

| Undervoltage Fault Filter                                             | 3.5        |       | 7.5   | μs       |                                                                                                                                                           |

| UV Propagation Delay                                                  |            | 5     | 8     | μs       | UV low to GATE pull-down active                                                                                                                           |

| UVL/UVH Input Current                                                 |            | 1     | 50    | nA       | ovion to ovii pain down delive                                                                                                                            |

| OV PIN—OVERVOLTAGE DETECTION                                          |            | •     |       | 1        |                                                                                                                                                           |

| Overvoltage Rising Threshold, Vovr                                    | 0.99       | 1.0   | 1.01  | V        |                                                                                                                                                           |

| Overvoltage Hysteresis Current                                        | 4.3        | 5     | 5.7   | μA       |                                                                                                                                                           |

| Overvoltage Fault Filter                                              | 1.75       | 5     | 3.75  | μs       |                                                                                                                                                           |

| OV Propagation Delay                                                  | 1.75       | 2     | 4     | μs       | OV high to GATE pull-down active                                                                                                                          |

| OV Input Current                                                      |            | 1     | 50    | nA       | OV High to GATE pull-down active                                                                                                                          |

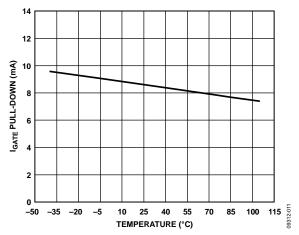

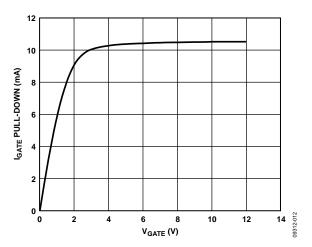

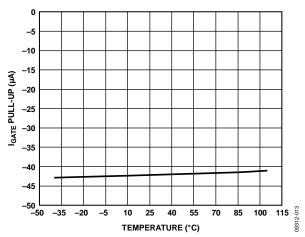

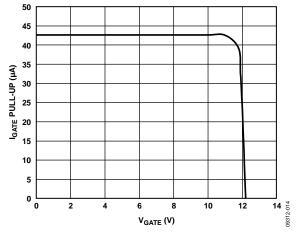

| GATE PIN                                                              |            | '     | 30    | IIA      |                                                                                                                                                           |

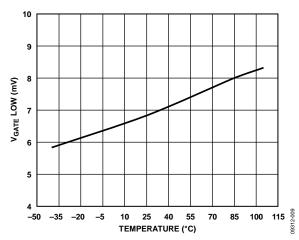

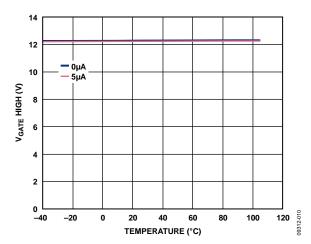

|                                                                       | 11         | 12    | 13    | V        | $I_{GATE} = -1.0 \mu\text{A}$                                                                                                                             |

| Gate Voltage High<br>Gate Voltage Low                                 | ''         | 10    | 100   | mV       | $I_{GATE} = -1.0 \mu\text{A}$ $I_{GATE} = 100 \mu\text{A}$                                                                                                |

| _                                                                     |            | 10    |       |          | 1                                                                                                                                                         |

| Pull-Up Current                                                       | -50<br>100 |       | -30   | μΑ       | $V_{GATE} = 0 \text{ V to } 8 \text{ V}; V_{SS} = 2 \text{ V}$                                                                                            |

| Pull-Down Current (Regulation)                                        | 100        | 10    |       | μΑ       | $V_{GATE} \ge 2V$                                                                                                                                         |

| Pull-Down Current (UV/OV/OC)                                          | 5          | 10    | 2000  | mA       | $V_{GATE} \ge 2 V$                                                                                                                                        |

| Pull-Down Current (Severe OC)                                         | 750        | 1500  | 2000  | mA       | $V_{GATE} \ge 6 V$                                                                                                                                        |

| Pull-Down On-Time (Severe OC)                                         | 8          | 20    | 16    | μs       | 0.77 * 1/101 * 0.237                                                                                                                                      |

| Gate Hold-Off Resistance                                              |            | 20    |       | Ω        | 0 V ≤ VIN ≤ 9.2 V                                                                                                                                         |

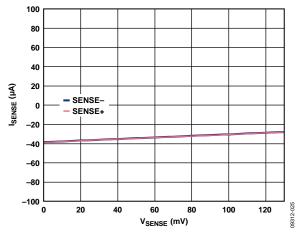

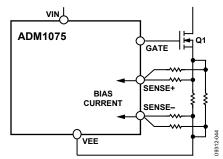

| SENSE+, SENSE– SENSE+, SENSE– Input Current, I <sub>SENSEx</sub>      |            |       | 100   | μΑ       | $V_{SENSE} \le 65 \text{ mV for ADM1075-1, per individual pin;}$ $V_{SENSE} \le 130 \text{ mV for ADM1075-2, per individual pin}$                         |

| SENSE+, SENSE– Input Imbalance, IASENSEX                              |            |       | 1     | μΑ       | $I_{\Delta SENSEx} = I_{SENSE+} - I_{SENSE-}$                                                                                                             |

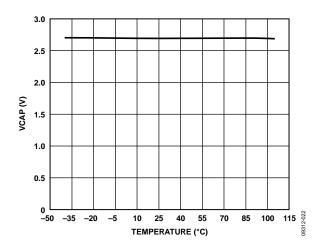

| VCAP                                                                  |            |       |       |          |                                                                                                                                                           |

| Internally Regulated Voltage, V <sub>VCAP</sub>                       | 2.66       | 2.7   | 2.74  | V        | $0 \le I_{VCAP} \le 100 \mu\text{A}$ ; $C_{VCAP} = 1 \mu\text{F}$                                                                                         |

| ISET                                                                  | 2.00       |       | 2., . | •        | O = IVEAR = 100 pt y evear 1 pt                                                                                                                           |

| ISET Reference Select Threshold, VISETRSTH                            | 1.35       | 1.5   | 1.65  | V        | If V <sub>ISET</sub> > V <sub>ISETRSTH</sub> an internal 1 V reference (V <sub>CLREF</sub> ) is used                                                      |

| ISET Internal Reference, V <sub>CLREF</sub>                           | 1.55       | 1.5   | 1.05  | ľ        | Accuracies included in total sense voltage accuracies                                                                                                     |

| Gain of Current Sense Amplifier, AV <sub>CSAMP</sub>                  |            | 50/25 |       | V<br>V/V | Accuracies included in total sense voltage accuracies  Accuracies included in total sense voltage accuracies                                              |

|                                                                       |            | 30/23 | 100   |          | _                                                                                                                                                         |

| ISET Input Current, I <sub>ISET</sub> ADM1075-1 ONLY (GAIN = 50)      |            |       | 100   | nA       | V <sub>ISET</sub> ≤ VCAP                                                                                                                                  |

|                                                                       |            |       |       |          |                                                                                                                                                           |

| Hot Swap Sense Voltage Hot Swap Sense Voltage Current Limit, Vsensect | 19.4       | 20    | 20.6  | mV       | $V_{ISET} > 1.65 \text{ V; } V_{GATE} = 3 \text{ V; } I_{GATE} = 0  \mu\text{A; } V_{SS} \geq 2 \text{ V; } V_{PLIM} = 0 \text{ V}$                       |

|                                                                       | 24.5       | 25    | 25.5  | mV       | $V_{ISET} = 1.25 \text{ V}; V_{GATE} = 3 \text{ V}; I_{GATE} = 0  \mu\text{A}; V_{SS} \ge 2 \text{ V}; V_{PLIM} = 0 \text{ V}$                            |

|                                                                       | 19.5       | 20    | 20.5  | mV       | VISET = 1.25 V, VGATE = 3 V, IGATE = 0 $\mu$ A, VSS $\geq$ 2 V, VPLIM = 0 V                                                                               |

|                                                                       | 14.5       | 15    | 15.5  | mV       | VISET = 1.0 V, VGATE = 3 V, IGATE = 0 $\mu$ A, VSS $\geq$ 2 V, VPLIM = 0 V<br>VISET = 0.75 V; VGATE = 3 V; IGATE = 0 $\mu$ A; VSS $\geq$ 2 V; VPLIM = 0 V |

|                                                                       | 14.5       | 13    | 13.3  | 1117     | VIDET $-0.73$ V, VGATE $-3$ V, IGATE $= 0 \mu A$ , VSS $\ge 2 V$ , VPLIM $= 0 V$                                                                          |

| Parameter                                                  | Min  | Тур  | Max  | Unit | Test Conditions/Comments                                                                                                              |

|------------------------------------------------------------|------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| Constant Power Active                                      | 9.4  | 10   | 11.0 | mV   | $V_{ISET} > 1.65 \text{ V; } V_{GATE} = 3 \text{ V; } I_{GATE} = 0  \mu\text{A; } V_{SS} \geq 2 \text{ V; } V_{PLIM} = 0.2 \text{ V}$ |

|                                                            | 4.5  | 5    | 5.7  | mV   | $V_{ISET} > 1.65 \text{ V}; V_{GATE} = 3 \text{ V}; I_{GATE} = 0  \mu\text{A}; V_{SS} \ge 2 \text{ V}; V_{PLIM} = 0.4 \text{ V}$      |

|                                                            | 1.4  | 2    | 2.6  | mV   | $V_{ISET} > 1.65 \text{ V}; V_{GATE} = 3 \text{ V}; I_{GATE} = 0  \mu\text{A}; V_{SS} \ge 2 \text{ V}; V_{PLIM} = 1.2 \text{ V}$      |

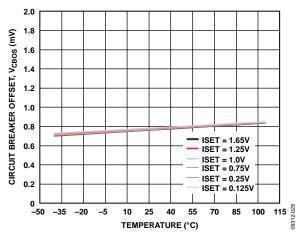

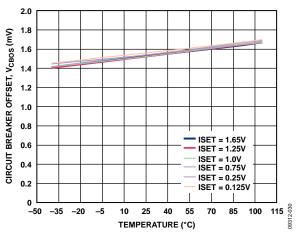

| Circuit Breaker Offset, V <sub>CBOS</sub>                  | 0.6  | 0.75 | 0.95 | mV   | Circuit breaker voltage, V <sub>CB</sub> = V <sub>SENSECL</sub> - V <sub>CBOS</sub>                                                   |

| Severe Overcurrent                                         |      |      |      |      | Activates high current gate pull-down                                                                                                 |

| Voltage Threshold, V <sub>SENSEOC</sub>                    | 23   | 25   | 27   | mV   | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; \text{ optional select through PMBus}$                                            |

|                                                            | 28   | 30   | 32   | mV   | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; \text{ default at power-up}$                                                      |

|                                                            | 38   | 40   | 42   | mV   | V <sub>ISET</sub> > 1.65 V; V <sub>SS</sub> ≥ 2 V; optional select through PMBus                                                      |

|                                                            | 43   | 45   | 47   | mV   | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; optional select through PMBus}$                                                   |

| Response Time                                              |      |      |      |      |                                                                                                                                       |

| Glitch Filter Duration                                     | 50   |      | 200  | ns   | $V_{ISET} > 1.65 \text{ V}$ ; $V_{SS} \ge 2 \text{ V}$ ; $V_{SENSE}$ step from 18 mV to 52 mV; optional select through PMBus          |

|                                                            | 500  |      | 900  | ns   | $V_{ISET} > 1.65 \text{ V; } V_{SS} \ge 2 \text{ V; } V_{SENSE} \text{ step from 18 mV to 52 mV;}$ default at power-up                |

|                                                            | 6.2  |      | 10.7 | μs   | $V_{ISET} > 1.65 \text{ V; } V_{SS} \ge 2 \text{ V; } V_{SENSE} \text{ step from 18 mV to 52 mV;}$ optional select through PMBus      |

|                                                            | 44   |      | 57   | μs   | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; V_{SENSE} \text{ step from 18 mV to 52 mV};$ optional select through PMBus        |

| Total Response Time                                        | 180  |      | 300  | ns   | V <sub>ISET</sub> > 1.65 V; V <sub>SS</sub> ≥ 2 V; V <sub>SENSE</sub> step from 18 mV to 52 mV; optional select through PMBus         |

|                                                            | 610  |      | 950  | ns   | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; V_{SENSE} \text{ step from 18 mV to 52 mV};$ default at power-up                  |

|                                                            | 7    |      | 13   | μs   | $V_{ISET} > 1.65 \text{ V; } V_{SS} \ge 2 \text{ V; } V_{SENSE} \text{ step from 18 mV to 52 mV;}$ optional select through PMBus      |

|                                                            | 45   |      | 60   | μs   | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; V_{SENSE} \text{ step from 18 mV to 52 mV};$ optional select through PMBus        |

| ADM1075-2 ONLY (GAIN = 25)                                 |      |      |      |      |                                                                                                                                       |

| Hot Swap Sense Voltage                                     |      |      |      |      |                                                                                                                                       |

| Hot Swap Sense Voltage Current Limit, V <sub>SENSECL</sub> | 39.2 | 40   | 40.8 | mV   | $V_{ISET} > 1.65 \text{ V; } V_{GATE} = 3 \text{ V; } I_{GATE} = 0  \mu\text{A; } V_{SS} \geq 2 \text{ V; } V_{PLIM} = 0 \text{ V}$   |

|                                                            | 49.2 | 50   | 50.8 | mV   | $V_{ISET} = 1.25 \text{ V}; V_{GATE} = 3 \text{ V}; I_{GATE} = 0  \mu\text{A}; V_{SS} \ge 2 \text{ V}; V_{PLIM} = 0 \text{ V}$        |

|                                                            | 39.2 | 40   | 40.8 | mV   | $V_{ISET} = 1.0 \text{ V}; V_{GATE} = 3 \text{ V}; I_{GATE} = 0  \mu\text{A}; V_{SS} \ge 2 \text{ V}; V_{PLIM} = 0 \text{ V}$         |

|                                                            | 29.2 | 30   | 30.8 | mV   | $V_{ISET} = 0.75 \text{ V}; V_{GATE} = 3 \text{ V}; I_{GATE} = 0  \mu\text{A}; V_{SS} \ge 2 \text{ V}; V_{PLIM} = 0 \text{ V}$        |

| Constant Power Active                                      | 19   | 20   | 21.9 | mV   | $V_{ISET} > 1.65 \text{ V}; V_{GATE} = 3 \text{ V}; I_{GATE} = 0  \mu\text{A}; V_{SS} \ge 2 \text{ V}; V_{PLIM} = 0.2 \text{ V}$      |

|                                                            | 9.2  | 10   | 11.2 | mV   | $V_{ISET} > 1.65 \text{ V}; V_{GATE} = 3 \text{ V}; I_{GATE} = 0  \mu\text{A}; V_{SS} \ge 2 \text{ V}; V_{PLIM} = 0.4 \text{ V}$      |

|                                                            | 3    | 4    | 5.0  | mV   | $V_{ISET} > 1.65 \text{ V}; V_{GATE} = 3 \text{ V}; I_{GATE} = 0  \mu\text{A}; V_{SS} \ge 2 \text{ V}; V_{PLIM} = 1.2 \text{ V}$      |

| Circuit Breaker Offset, VCBOS                              | 1.1  | 1.5  | 1.9  | mV   | Circuit breaker voltage, V <sub>CB</sub> = V <sub>SENSECL</sub> - V <sub>CBOS</sub>                                                   |

| Severe Overcurrent                                         |      |      |      |      | Activates high current gate pull-down                                                                                                 |

| Voltage Threshold, Vsenseoc1                               | 46   | 50   | 54   | mV   | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; optional select through PMBus}$                                                   |

|                                                            | 56   | 60   | 64   | mV   | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; default at power-up}$                                                             |

|                                                            | 76   | 80   | 84   | mV   | V <sub>ISET</sub> > 1.65 V; V <sub>SS</sub> ≥ 2 V; optional select through PMBus                                                      |

|                                                            | 86   | 90   | 94   | mV   | V <sub>ISET</sub> > 1.65 V; V <sub>SS</sub> ≥ 2 V; optional select through PMBus                                                      |

| Response Time                                              |      |      |      |      |                                                                                                                                       |

| Glitch Filter Duration                                     | 50   |      | 200  | ns   | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; V_{SENSE} \text{ step from 36 mV to 104 mV};$ optional select through PMBus       |

|                                                            | 400  |      | 900  | ns   | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; V_{SENSE} \text{ step from 36 mV to 104 mV};$ default at power-up                 |

|                                                            | 6.2  |      | 10.7 | μs   | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; V_{SENSE} \text{ step from 36 mV to 104 mV};$ optional select through PMBus       |

|                                                            | 44   |      | 57   | μs   | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; V_{SENSE} \text{ step from 36 mV to 104 mV};$ optional select through PMBus       |

| Parameter                                     | Min   | Тур  | Max         | Unit     | Test Conditions/Comments                                                                                                                      |

|-----------------------------------------------|-------|------|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Total Response Time                           | 180   |      | 300         | ns       | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; V_{SENSE} \text{ step from 36 mV to 104 mV};$                                             |

|                                               |       |      |             |          | optional select through PMBus                                                                                                                 |

|                                               | 610   |      | 950         | ns       | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; V_{SENSE}$ step from 36 mV to 104 mV; default at power-up                                 |

|                                               | 7     |      | 13          | μs       | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; V_{SENSE}$ step from 36 mV to 104 mV; optional select through PMBus                       |

|                                               | 45    |      | 60          | μs       | $V_{ISET} > 1.65 \text{ V}; V_{SS} \ge 2 \text{ V}; V_{SENSE} \text{ step from 36 mV to 104 mV};$ optional select through PMBus               |

| SOFT START                                    |       |      |             |          | optional sciect throught mous                                                                                                                 |

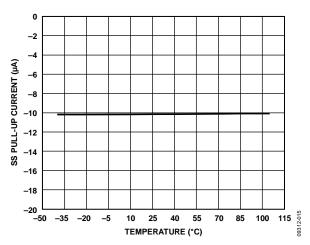

| SS Pull-Up Current, Iss                       | -11.5 | -10  | -8.5        | μA       | $V_{SS} = 0V$                                                                                                                                 |

| Default V <sub>SENSECL</sub> Limit            | 0.6   | 1.25 | -8.5<br>1.9 | mV       | When V <sub>SENSE</sub> reaches this level, I <sub>SS</sub> is enabled, ramping;                                                              |

| Detault VSENSECL EITHE                        | 0.0   | 1.23 | 1.5         | ''''     | $V_{SS} = 0$ V; ADM1075-1 only (gain = 50)                                                                                                    |

|                                               | 1.2   | 2.5  | 3.8         | mV       | When $V_{SENSE}$ reaches this level, $I_{SS}$ is enabled, ramping; $V_{SS} = 0$ V; ADM1075-2 only (gain = 25)                                 |

| SS Pull-Down Current                          |       | 100  |             | μΑ       | $V_{SS} = 1 \text{ V}$                                                                                                                        |

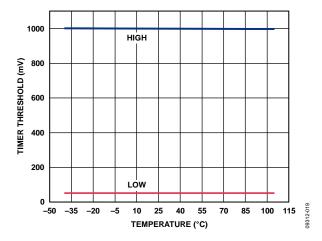

| TIMER                                         |       |      |             |          |                                                                                                                                               |

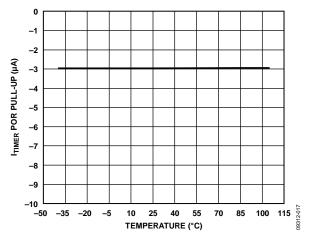

| Timer Pull-Up Current (POR), ITIMERUPPOR      | -4    | -3   | -2          | μΑ       | Initial power-on reset; V <sub>TIMER</sub> = 0.5 V                                                                                            |

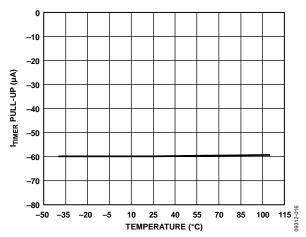

| Timer Pull-Up Current (OC Fault), ITIMERUPFLT | -63   | -60  | -57         | μΑ       | Overcurrent fault; 0.05 V ≤ V <sub>TIMER</sub> ≤ 1 V                                                                                          |

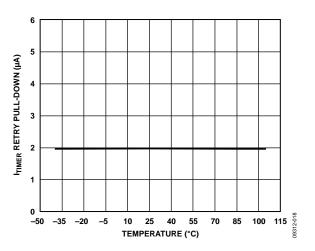

| Timer Pull-Down Current (Retry), ITIMERDNRT   | 1.7   | 2    | 2.3         | μA       | After a fault when GATE is off; $V_{TIMER} = 0.5 \text{ V}$                                                                                   |

| Timer Retry/OC Fault Current Ratio            |       | 3.33 |             | %        | Defines the limits of the autoretry duty cycle                                                                                                |

| Timer Pull-Down Current (Hold), ITIMERDNHOLD  |       | 100  |             | μA       | Holds TIMER at 0 V when inactive; V <sub>TIMER</sub> = 0.5 V                                                                                  |

| Timer High Threshold, V <sub>TIMERH</sub>     | 0.98  | 1.0  | 1.02        | v        | ,                                                                                                                                             |

| Timer Low Threshold, V <sub>TIMERL</sub>      | 0.03  | 0.05 | 0.07        | V        |                                                                                                                                               |

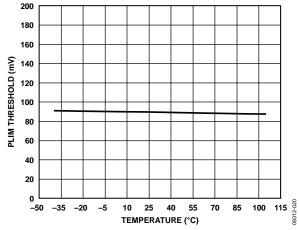

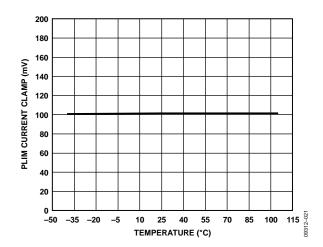

| PLIM                                          |       |      |             |          |                                                                                                                                               |

| PLIM Active Threshold                         | 0.08  | 0.09 | 0.1         | V        | V <sub>ISET</sub> > 1.65 V                                                                                                                    |

| Input Current, Iplim                          | 0.00  | 0.05 | 100         | nA       | V <sub>PLIM</sub> ≤ 1 V                                                                                                                       |

| Minimum Current Clamp, VICLAMP                | 75    | 100  | 125         | mV       | $V_{PLIM} = 1.2 \text{ V; } V_{SENSE\_IMIN} = (V_{ICLAMP} \div \text{gain}) = \text{minimum}$                                                 |

| Willimum Current Clamp, Victamp               | /3    | 100  | 123         | IIIV     | allowed current control                                                                                                                       |

| DRAIN                                         |       |      |             |          |                                                                                                                                               |

| DRAIN Voltage at Which PWRGD Asserts          | 1.9   | 2    | 2.1         | V        | I <sub>DRAIN</sub> ≤ 50 μA                                                                                                                    |

| ADC_AUX/ADC_V                                 |       |      |             |          |                                                                                                                                               |

| Input Current                                 |       |      | 100         | nA       | $0 \text{ V} \leq \text{V}_{ADC} \leq 1.5 \text{ V}$                                                                                          |

| SHDN PIN                                      |       |      |             |          |                                                                                                                                               |

| Input High Voltage, V <sub>IH</sub>           | 1.1   |      |             | V        |                                                                                                                                               |

| Input Low Voltage, V <sub>IL</sub>            |       |      | 0.8         | V        |                                                                                                                                               |

| Glitch Filter                                 |       | 1    |             | μs       |                                                                                                                                               |

| Internal Pull-Up Current                      |       | 8    |             | μA       | Pull-up to VIN                                                                                                                                |

| RESTART PIN                                   |       |      |             |          |                                                                                                                                               |

| Input High Voltage, V <sub>IH</sub>           | 1.1   |      |             | V        |                                                                                                                                               |

| Input Low Voltage, V <sub>IL</sub>            |       |      | 0.8         | V        |                                                                                                                                               |

| Glitch Filter                                 |       | 1    |             | μs       |                                                                                                                                               |

| Internal Pull-Up Current                      |       | 8    |             | μΑ       | Pull-up to VIN                                                                                                                                |

| SPLYGD PIN                                    |       |      |             | P        |                                                                                                                                               |

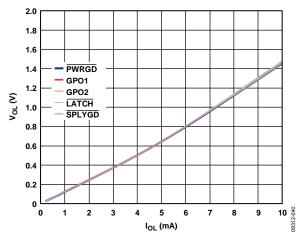

| Output Low Voltage, Vollatch                  |       |      | 0.4         | V        | Isprygp = 1 mA                                                                                                                                |

| Output Low Voltage, Vol_LATCH                 |       |      | 1.5         | V        | $I_{SPLYGD} = 1 \text{ IIIA}$ $I_{SPLYGD} = 5 \text{ mA}$                                                                                     |

| Looko ao Current                              |       |      | 1.5         |          |                                                                                                                                               |

| Leakage Current                               |       |      | 100         | nA<br>μA | $V_{SPLYGD} \le 2 \text{ V}; \overline{SPLYGD} \text{ pin disabled}$<br>$V_{SPLYGD} \le 14 \text{ V}; \overline{SPLYGD} \text{ pin disabled}$ |

| LATCH PIN                                     |       |      | •           | μ, ,     | Variety 2 11 V, St E1 30 pm disabled                                                                                                          |

|                                               |       |      | 0.4         | W        |                                                                                                                                               |

| Output Low Voltage, Vol_LATCH                 |       |      | 0.4         | V        | I <sub>LATCH</sub> = 1 mA                                                                                                                     |

| Lashana Comerci                               |       |      | 1.5         | V        | I <sub>LATCH</sub> = 5 mA                                                                                                                     |

| Leakage Current                               |       |      | 100         | nA       | V <sub>LATCH</sub> ≤ 2 V; LATCH pin disabled                                                                                                  |

|                                               |       |      | 1           | μΑ       | V <sub>LATCH</sub> ≤ 14 V; LATCH pin disabled                                                                                                 |

| GPO1/ALERT1/CONV PIN                          |       |      |             |          |                                                                                                                                               |

| Output Low Voltage, Vol_GPO1                  |       |      | 0.4         | V        | $I_{GPO} = 1 \text{ mA}$                                                                                                                      |

|                                               | 1     |      | 1.5         | V        | $I_{GPO} = 5 \text{ mA}$                                                                                                                      |

| Parameter                                | Min  | Тур   | Max   | Unit | Test Conditions/Comments                                                                     |

|------------------------------------------|------|-------|-------|------|----------------------------------------------------------------------------------------------|

| Leakage Current                          |      |       | 100   | nA   | V <sub>GPO</sub> ≤ 2 V; GPO disabled                                                         |

|                                          |      |       | 1     | μΑ   | V <sub>GPO</sub> = 14 V; GPO disabled                                                        |

| Input High Voltage, V <sub>IH</sub>      | 1.1  |       |       | V    | Configured as CONV pin                                                                       |

| Input Low Voltage, V <sub>IL</sub>       |      |       | 0.8   | V    | Configured as CONV pin                                                                       |

| Glitch Filter                            |      | 1     |       | μs   | Configured as CONV pin                                                                       |

| GPO2/ALERT2 PIN                          |      |       |       |      |                                                                                              |

| Output Low Voltage, Vol_GPO2             |      |       | 0.4   | V    | $I_{GPO} = 1 \text{ mA}$                                                                     |

| ,                                        |      |       | 1.5   | V    | $I_{GPO} = 5 \text{ mA}$                                                                     |

| Leakage Current                          |      |       | 100   | nA   | V <sub>GPO</sub> ≤ 2 V; GPO disabled                                                         |

| <u> </u>                                 |      |       | 1     | μΑ   | V <sub>GPO</sub> = 14 V; GPO disabled                                                        |

| PWRGD PIN                                |      |       |       |      |                                                                                              |

| Output Low Voltage, Vol_PWRGD            |      |       | 0.4   | V    | $I_{PWRGD} = 1 \text{ mA}$                                                                   |

| 1 37 7 = 77                              |      |       | 1.5   | V    | $I_{PWRGD} = 5 \text{ mA}$                                                                   |

| VIN That Guarantees Valid Output         | 1    |       |       | V    | $I_{SINK} = 100 \mu\text{A};  V_{OL\_PWRGD} = 0.4 \text{V}$                                  |

| Leakage Current                          |      |       | 100   | nA   | $V_{PWRGD} \le 2 \text{ V}; \overline{PWRGD} \text{ active}$                                 |

| •                                        |      |       | 1     | μΑ   | V <sub>PWRGD</sub> = 14 V; <del>PWRGD</del> active                                           |

| CURRENT AND VOLTAGE MONITORING           |      |       |       | F    | VPWRGD = 11 V, · · · · · · · · · · · · · · · · · ·                                           |

| Current Sense Absolute Error (ADM1075-1) |      |       |       |      | 25 mV input range; 128 sample averaging (unless                                              |

| Current Sense Absolute Error (Abwro75 1) |      |       |       |      | otherwise noted)                                                                             |

|                                          |      | -0.01 | ±0.7  | %    | $V_{SENSE} = 25 \text{ mV}$                                                                  |

|                                          |      | 0.05  | ±0.85 | %    | $V_{SENSF} = 20 \text{ mV}$                                                                  |

|                                          |      | 0.07  | ±0.85 | %    | $V_{\text{SENSE}} = 20 \text{ mV}$ ; 16 sample averaging                                     |

|                                          |      | 0.04  | ±2.8  | %    | V <sub>SENSE</sub> = 20 mV; 1 sample averaging                                               |

|                                          |      |       | ±1.0  | %    | $V_{SENSE} = 15 \text{ mV}$                                                                  |

|                                          |      |       | ±1.4  | %    | $V_{SENSE} = 10 \text{ mV}$                                                                  |

|                                          |      |       | ±2.7  | %    | $V_{\text{SENSE}} = 5 \text{ mV}$                                                            |

|                                          |      |       | ±5.9  | %    | $V_{SENSE} = 2.5 \text{ mV}$                                                                 |

| Current Sense Absolute Error (ADM1075-2) |      |       |       |      | 50 mV input range; 128 sample averaging (unless otherwise noted)                             |

|                                          |      | -0.03 | ±0.65 | %    | $V_{SENSE} = 50 \text{ mV}$                                                                  |

|                                          |      | -0.03 | ±0.7  | %    | $V_{SENSE} = 40 \text{ mV}$                                                                  |

|                                          |      | -0.03 | ±0.7  | %    | V <sub>SENSE</sub> = 40 mV; 16 sample averaging                                              |

|                                          |      | -0.04 | ±1.35 | %    | $V_{\text{SENSE}} = 40 \text{ mV}$ ; 1 sample averaging                                      |

|                                          |      |       | ±0.75 | %    | $V_{SENSE} = 30 \text{ mV}$                                                                  |

|                                          |      |       | ±0.9  | %    | $V_{SENSE} = 20 \text{ mV}$                                                                  |

|                                          |      |       | ±1.7  | %    | $V_{SENSE} = 10 \text{ mV}$                                                                  |

|                                          |      |       | ±3.0  | %    | $V_{SENSE} = 5 \text{ mV}$                                                                   |

| ADC_V/ADC_AUX Absolute Accuracy          | -0.8 |       | +0.8  | %    | $0.6 \text{ V} \le \text{V}_{ADC} \le 1.5 \text{ V}$                                         |

| ADC Conversion Time                      |      |       |       |      | 1 sample of voltage and current; from command received to valid data in register             |

|                                          |      | 191   | 219   | μs   | VAUX disabled                                                                                |

|                                          |      | 263   | 301   | μs   | VAUX enabled                                                                                 |

|                                          |      |       |       |      | 16 samples of voltage and current averaged; from command received to valid data in register  |

|                                          |      | 2.830 | 3.243 | ms   | VAUX disabled                                                                                |

|                                          |      | 3.987 | 4.568 | ms   | VAUX enabled                                                                                 |

|                                          |      |       |       |      | 128 samples of voltage and current averaged; from command received to valid data in register |

|                                          |      | 22.54 | 25.83 | ms   | VAUX disabled (default on power-up)                                                          |

|                                          |      | 31.79 | 36.43 | ms   | VAUX enabled                                                                                 |

| Power Multiplication Time                |      | 14    |       | μs   |                                                                                              |

| Parameter                                    | Min | Тур | Max | Unit | Test Conditions/Comments                                                                        |

|----------------------------------------------|-----|-----|-----|------|-------------------------------------------------------------------------------------------------|

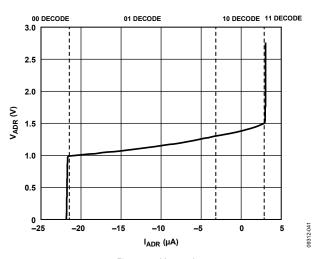

| ADR PIN                                      |     |     |     |      | See Table 6                                                                                     |

| Address Set to 00                            | 0   |     | 0.8 | V    | Connect to VEE                                                                                  |

| Input Current for Address 00                 | -40 | -22 |     | μΑ   | $V_{ADR} = 0 \text{ V to } 0.8 \text{ V}$                                                       |

| Address Set to 01                            | 135 | 150 | 165 | kΩ   | Resistor to VEE                                                                                 |

| Address Set to 10                            | -1  |     | +1  | μΑ   | No connect state; maximum leakage current allowed                                               |

| Address Set to 11                            | 2.1 |     |     | V    | Connect to VCAP                                                                                 |

| Input Current for Address 11                 |     | 3   | 10  | μΑ   | $V_{ADR} = 2.0 \text{ V}$ to VCAP; must not exceed the maximum allowable current draw from VCAP |

| SERIAL BUS DIGITAL INPUTS (SDAI/SDAO, SCL)   |     |     |     |      |                                                                                                 |

| Input High Voltage, V <sub>IH</sub>          | 1.1 |     |     | V    |                                                                                                 |

| Input Low Voltage, V <sub>I</sub> L          |     |     | 0.8 | V    |                                                                                                 |

| Output Low Voltage, Vol                      |     |     | 0.4 | V    | I <sub>OL</sub> = 4 mA, SDAO only                                                               |

| Input Leakage, I <sub>LEAK-PIN</sub>         | -10 |     | +10 | μΑ   |                                                                                                 |

|                                              | -5  |     | +5  | μΑ   | Device is not powered                                                                           |

| Nominal Bus Voltage, VDD                     | 2.7 |     | 5.5 | V    | 3 V to 5 V ±10%                                                                                 |

| Capacitive Load per Bus Segment, CBUS        |     |     | 400 | рF   |                                                                                                 |

| Capacitance for SDAI, SDAO, or SCL Pin, CPIN |     | 5   |     | рF   |                                                                                                 |

| Input Glitch Filter, t <sub>SP</sub>         | 0   |     | 50  | ns   |                                                                                                 |

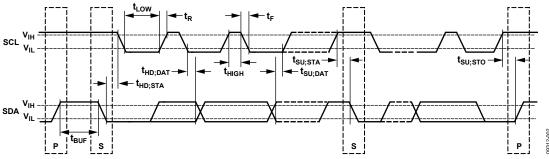

### **SERIAL BUS TIMING**

Table 2.

| Parameter           | Description                            | Min                         | Тур | Max | Unit | Test Conditions/Comments |

|---------------------|----------------------------------------|-----------------------------|-----|-----|------|--------------------------|

| f <sub>SCLK</sub>   | Clock frequency                        |                             |     | 400 | kHz  |                          |

| t <sub>BUF</sub>    | Bus free time                          | 1.3                         |     |     | μs   |                          |

| t <sub>HD;STA</sub> | Start hold time                        | 0.6                         |     |     | μs   |                          |

| t <sub>SU;STA</sub> | Start setup time                       | 0.6                         |     |     | μs   |                          |

| t <sub>SU;STO</sub> | Stop setup time                        | 0.6                         |     |     | μs   |                          |

| t <sub>HD;DAT</sub> | SDA <sup>1</sup> hold time             | 300                         |     | 900 | ns   |                          |

| t <sub>SU;DAT</sub> | SDA <sup>1</sup> setup time            | 100                         |     |     | ns   |                          |

| t <sub>LOW</sub>    | SCL low time                           | 1.3                         |     |     | μs   |                          |

| t <sub>HIGH</sub>   | SCL high time                          | 0.6                         |     |     | μs   |                          |

| $t_R^2$             | SCL, SDA <sup>1</sup> rise time        | 20                          |     | 300 | ns   |                          |

| t <sub>F</sub>      | SCL, SDA <sup>1</sup> fall time        | 20                          |     | 300 | ns   |                          |

| tor                 | SCL, SDA <sup>1</sup> output fall time | 20 + 0.1 × C <sub>BUS</sub> |     | 250 | ns   |                          |

$<sup>^1</sup>$  SDAI and SDAO tied together.  $^2$  t<sub>R</sub> = (V<sub>IL(MAX)</sub> - 0.15) to (V<sub>IH3V3</sub> + 0.15) and t<sub>F</sub> = 0.9 V<sub>DD</sub> to (V<sub>IL(MAX)</sub> - 0.15); where V<sub>IH3V3</sub> = 2.1 V, and V<sub>DD</sub> = 3.3 V.

Figure 2. Serial Bus Timing Diagram

### **ABSOLUTE MAXIMUM RATINGS**

Table 3

| Table 3.                                |                            |  |  |

|-----------------------------------------|----------------------------|--|--|

| Parameter                               | Rating                     |  |  |

| VIN Pin to VEE                          | -0.3 V to +14 V            |  |  |

| UVL Pin to VEE                          | -0.3 V to +4 V             |  |  |

| UVH Pin to VEE                          | −0.3 V to +4 V             |  |  |

| OV Pin to VEE                           | -0.3 V to +4 V             |  |  |

| ADC_V Pin to VEE                        | −0.3 V to +4 V             |  |  |

| ADC_AUX Pin to VEE                      | −0.3 V to +4 V             |  |  |

| SS Pin to VEE                           | -0.3  V to (VCAP + 0.3  V) |  |  |

| TIMER Pin to VEE                        | -0.3  V to (VCAP + 0.3  V) |  |  |

| VCAP Pin to VEE                         | −0.3 V to +4 V             |  |  |

| ISET Pin to VEE                         | −0.3 V to +4 V             |  |  |

| SPLYGD Pin to VEE                       | -0.3 V to +18 V            |  |  |

| LATCH Pin to VEE                        | -0.3 V to +18 V            |  |  |

| RESTART Pin to VEE                      | –0.3 V to +18 V            |  |  |

| SHDN Pin to VEE                         | –0.3 V to +18 V            |  |  |

| PWRGD Pin to VEE                        | –0.3 V to +18 V            |  |  |

| DRAIN Pin to VEE                        | -0.3 V to (VCAP + 0.3 V)   |  |  |

| SCL Pin to VEE                          | −0.3 V to +6.5 V           |  |  |

| SDAI Pin to VEE                         | –0.3 V to +6.5 V           |  |  |

| SDAO Pin to VEE                         | −0.3 V to +6.5 V           |  |  |

| ADR Pin to VEE                          | -0.3  V to (VCAP + 0.3  V) |  |  |

| GPO1/ALERT1/CONV Pin to VEE             | –0.3 V to +18 V            |  |  |

| GPO2/ALERT2 Pin to VEE                  | –0.3 V to +18 V            |  |  |

| PLIM Pin to VEE                         | −0.3 V to +4 V             |  |  |

| GATE Pin to VEE                         | -0.3 V to +18 V            |  |  |

| SENSE+ Pin to VEE                       | −0.3 V to +4 V             |  |  |

| SENSE – Pin to VEE                      | −0.3 V to +0.3 V           |  |  |

| VEE to VEE_G                            | −0.3 V to +0.3 V           |  |  |

| Continuous Current into Any Pin         | ±10 mA                     |  |  |

| Storage Temperature Range               | −65°C to +125°C            |  |  |

| Operating Junction Temperature<br>Range | −40°C to +105°C            |  |  |

| Lead Temperature, Soldering (10 sec)    | 300°C                      |  |  |

| Junction Temperature                    | 150°C                      |  |  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

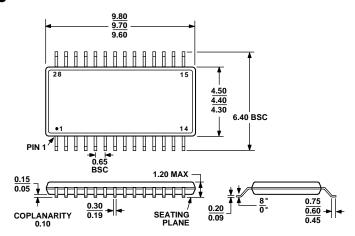

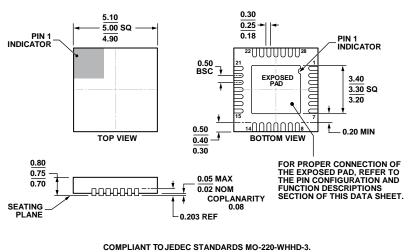

**Table 4. Thermal Resistance**

| Package Type  | $\theta_{JA}^1$ | θις | Unit |

|---------------|-----------------|-----|------|

| 28-Lead TSSOP | 68              | 20  | °C/W |

| 28-Lead LFCSP | 35              | 4   | °C/W |

<sup>&</sup>lt;sup>1</sup> Measured on JEDEC 4-layer board in still air.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

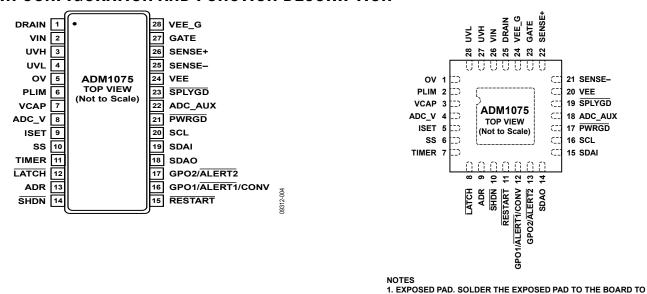

## PIN CONFIGURATION AND FUNCTION DESCRIPTION

Figure 3. TSSOP Pin Configuration

Figure 4. LFCSP Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin   | No.   |          |                                                                                                                                                                                                                                                                                                           |

|-------|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP | LFCSP | Mnemonic | Description                                                                                                                                                                                                                                                                                               |

| 1     | 25    | DRAIN    | Connect to the drain pin of the FET through a resistor. The current in this resistor is used to determine the V <sub>DS</sub> of the MOSFET. This is used for PWRGD.                                                                                                                                      |

| 2     | 26    | VIN      | Shunt Regulated Positive Supply to Chip. Connect to the positive supply rail via a shunt resistor. A 1 $\mu$ F capacitor to VEE is recommended on the VIN pin.                                                                                                                                            |

| 3     | 27    | UVH      | Undervoltage Rising Input Pin. An external resistor divider is used from the supply to this pin to allow an internal comparator to detect if the supply is under the UVH limit.                                                                                                                           |

| 4     | 28    | UVL      | Undervoltage Falling Input Pin. An external resistor divider is used from the supply to this pin to allow an internal comparator to detect if the supply is under the UVL limit.                                                                                                                          |

| 5     | 1     | OV       | Overvoltage Input Pin. An external resistor divider is used from the supply to this pin to allow an internal comparator to detect if the supply is above the OV limit.                                                                                                                                    |

| 6     | 2     | PLIM     | The voltage on this pin is proportional to the V <sub>DS</sub> voltage of the FET. As the PLIM voltage changes, the current limit automatically adjusts to maintain constant power across the FET.                                                                                                        |

| 7     | 3     | VCAP     | A capacitor with a value of 1 $\mu$ F or greater should be placed on this pin to maintain good accuracy. This is an internal regulated supply. This pin can be used as a reference to program the ISET pin voltage.                                                                                       |

| 8     | 4     | ADC_V    | This pin is used to read back the input voltage using the internal ADC. It can be connected to the OV string or a separate divider.                                                                                                                                                                       |

| 9     | 5     | ISET     | This pin allows the current limit threshold to be programmed. The default limit is set when this pin is connected directly to VCAP. Alternatively, using a resistor divider from VCAP, the current limit can be adjusted to achieve a user defined sense voltage. An external reference can also be used. |

| 10    | 6     | SS       | A capacitor is used on this pin to set the inrush current soft start ramp profile. The voltage on the soft start pin controls the current sense voltage limit, allowing control over the inrush current profile.                                                                                          |

| 11    | 7     | TIMER    | Timer Pin. An external capacitor, C <sub>TIMER</sub> , sets an initial timing cycle delay and a fault delay. The GATE pin turns off when the voltage on the TIMER pin exceeds the upper threshold.                                                                                                        |

| 12    | 8     | LATCH    | This pin signals the device latching off after an overcurrent fault. This pin is also used to configure the desired retry scheme. See the Hot Swap Fault Retry section for additional details.                                                                                                            |

| 13    | 9     | ADR      | PMBus Address Pin. This pin can be tied low, tied to VCAP, left floating, or tied low through a resistor to set four different PMBus addresses.                                                                                                                                                           |

| Pin   | No.   |                      |                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|-------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSSOP | LFCSP | Mnemonic             | Description                                                                                                                                                                                                                                                                                                                                                                                                        |

| 14    | 10    | SHDN                 | Drive this pin low to shut down the gate. Internal weak pull-up to VIN.  This pin is also used to configure the desired retry scheme. See the Hot Swap Fault Retry section for additional details.                                                                                                                                                                                                                 |

| 15    | 11    | RESTART              | Falling Edge Triggered 10 sec Automatic Restart. The gate remains off for 10 seconds, and then powers back up. Internal weak pull-up to VIN. This pin is also used to configure the desired retry scheme. See the Hot Swap Fault Retry section for additional details.                                                                                                                                             |

| 16    | 12    | GPO1/ALERT1<br>/CONV | General-Purpose Digital Output (GPO1).  Alert (ALERT1). This pin can be configured to generate an alert signal when one or more fault or warning conditions have been detected.  Conversion (CONV). This pin can be used as an input signal to control when a power monitor ADC sampling cycle begins.  This pin defaults to indicate FET health mode at power-up. There is no internal pull-up on this pin.       |

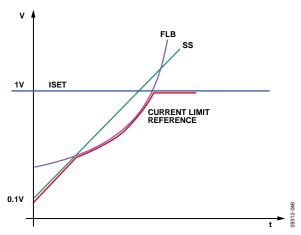

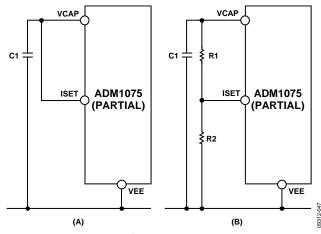

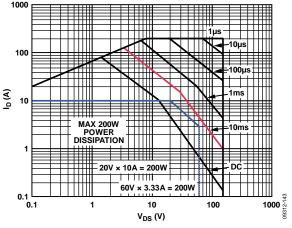

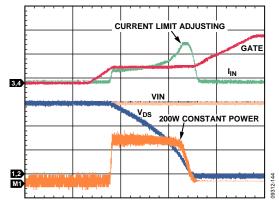

| 17    | 13    | GPO2/ALERT2          | General-Purpose Digital Output (GPO2).  Alert (ALERT2). This pin can be configured to generate an alert signal when one or more fault or warning conditions have been detected.  This pin is also used to configure the desired retry scheme. See the Hot Swap Fault Retry section for further details. This pin defaults to indicate a seven-attempt fail at power-up.  There is no internal pull-up on this pin. |