### **General Description**

The DS4026 is a temperature-compensated crystal oscillator (TCXO) that provides ±1ppm frequency stability over the -40°C to +85°C industrial temperature range. The DS4026 is also available in Stratum 3 versions (see the Ordering Information—Stratum 3 table). Each device is factory calibrated over temperature to achieve the ±1ppm frequency stability. Standard frequencies for the device include 10, 12.8, 19.44, 20, 38.88, 40, and 51.84MHz. Contact the factory for custom frequencies.

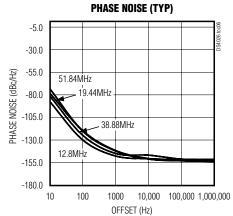

The DS4026 provides excellent phase-noise characteristics. The output is a push-pull CMOS square wave with symmetrical rise and fall times. In addition, the DS4026 is designed to provide a maximum frequency deviation of less than ±4.6ppm over 20 years. The device also provides an I<sup>2</sup>C interface to allow pushing and pulling of the output frequency by a minimum of ±8ppm (±5ppm for 10MHz) with typical 1ppb resolution.

The DS4026 implements a temperature-to-voltage conversion with a nonlinear relationship. The output from the temperature-to-voltage converter is used to drive the voltage-controlled crystal oscillator to compensate for frequency change.

The device implements an on-chip temperature sensor lookup table, and a digital-to-analog converter (DAC) to adjust the frequency. An I2C interface used to communicate with the DS4026 performs temperature readings and frequency push-pull.

#### **Applications**

Reference Clock Generation

Wireless

Telecom/Datacom/SATCOM

Test and Measurement

#### **Features**

- **♦** ±1ppm Frequency Accuracy Over -40°C to +85°C

- ♦ Standard Frequencies: 10, 12.8, 19.44, 20, 38.88, 40. 51.84MHz

- ♦ Stratum 3 Frequencies: 10, 12.8, 19.2, 20MHz

- ♦ Maximum ±4.6ppm Deviation Over 20 Years

- ♦ Minimum ±8ppm (±5ppm for 10MHz) Digital Frequency Tuning Through I<sup>2</sup>C Interface

- ♦ Surface-Mount 16-Pin SO Package

- **♦** Pb Free/RoHS Compliant

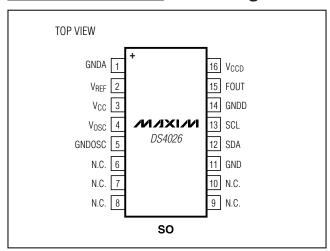

### Pin Configuration

### **Ordering Information**

| PART        | TEMP RANGE     | OUTPUT (f <sub>C</sub> )<br>(MHz, CMOS) | PIN-PACKAGE | TOP MARK*  |

|-------------|----------------|-----------------------------------------|-------------|------------|

| DS4026S+ACC | 0°C to +70°C   | 10.00                                   | 16 SO       | DS4026-ACC |

| DS4026S+ACN | -40°C to +85°C | 10.00                                   | 16 SO       | DS4026-ACN |

| DS4026S+BCC | 0°C to +70°C   | 12.80                                   | 16 SO       | DS4026-BCC |

| DS4026S+BCN | -40°C to +85°C | 12.80                                   | 16 SO       | DS4026-BCN |

| DS4026S+ECC | 0°C to +70°C   | 16.80                                   | 16 SO       | DS4026-ECC |

| DS4026S+ECN | -40°C to +85°C | 16.80                                   | 16 SO       | DS4026-ECN |

| DS4026S+FCC | 0°C to +70°C   | 16.384                                  | 16 SO       | DS4026-FCC |

| DS4026S+FCN | -40°C to +85°C | 16.384                                  | 16 SO       | DS4026-FCN |

#### Ordering Information continued at end of data sheet.

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

<sup>\*</sup>The top mark will include a "+" for a lead(Pb)-free/RoHS-compliant device.

#### **ABSOLUTE MAXIMUM RATINGS**

Voltage Range on V<sub>CC</sub>, V<sub>CCD</sub>, and V<sub>OSC</sub>

Relative to Ground......-0.3V to +3.8V

Voltage Range on SDA, SCL, and FOUT

Relative to Ground.....-0.3V to (V<sub>CC</sub> + 0.3V)

Operating Temperature Range (noncondensing)...-40°C to +85°C

Storage Temperature Range ....-40°C to +85°C

Soldering Temperature Range (noncondensing)...-40°C to +85°C

Storage Temperature Range (noncondensing)...-40°C to +85°C

Soldering Temperature Range (noncondensing)...-40°C to +85°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED DC OPERATING CONDITIONS

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER               | SYMBOL | CONDITIONS | MIN   | TYP | MAX   | UNITS |

|-------------------------|--------|------------|-------|-----|-------|-------|

| Power-Supply Voltage    | Vcc    |            | 3.135 | 3.3 | 3.465 | V     |

| Oscillator Power Supply | Vosc   |            | 3.135 | 3.3 | 3.465 | V     |

| Driver Power Supply     | Vccd   |            | 3.135 | 3.3 | 3.465 | V     |

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 3.135V \text{ to } 3.465V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Notes 1, 2, 3)

| PARAMETER                             | SYMBOL                         | CONDITIONS                                            | MIN          | TYP | MAX                        | UNITS |

|---------------------------------------|--------------------------------|-------------------------------------------------------|--------------|-----|----------------------------|-------|

| V <sub>CC</sub> Active-Supply Current | Icc                            | (Note 4)                                              |              | 1.5 | 2.5                        | mA    |

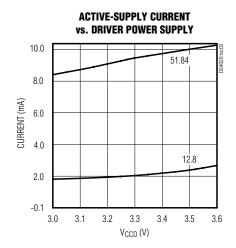

| Vosc Oscillator Active-Supply         | logo                           | FOUT CMOS output on, CL = 10pF, frequency < 25MHz     |              | 3   | 4                          | mA.   |

| Current                               | losc                           | FOUT CMOS output on, CL = 10pF, frequency ≥ 25MHz     |              | 5   | 9                          | IIIA  |

| V <sub>CCD</sub> Driver Active-Supply | loop                           | FOUT CMOS output on, CL = 10pF, frequency < 25MHz     |              | 2   | 3                          | mA    |

| Current                               | ICCD                           | FOUT CMOS output on, CL = 10pF, frequency ≥ 25MHz     |              | 3   | 5                          | IIIA  |

| SCL Input Leakage                     | ILI                            |                                                       | -1           |     | +1                         | μΑ    |

| SDA Leakage                           | ILO                            | Output off                                            | -1           |     | +1                         | μΑ    |

| SCL, SDA High Input Voltage           | VIH                            |                                                       | 0.7 x<br>VCC |     | V <sub>C</sub> C<br>+ 0.3  | V     |

| SCL, SDA Low Input Voltage            | VIL                            |                                                       | -0.3         |     | +0.3 x<br>V <sub>C</sub> C | V     |

| SDA Logic 0 Output                    | loL                            | V <sub>CC</sub> = 3.0V, V <sub>OL</sub> = 0.4V        |              |     | 3                          | mA    |

| FOUT High Output Voltage              | Voh                            | V <sub>CCD</sub> = 3V, I <sub>OH</sub> = -2mA         | 2.4          |     |                            | V     |

| FOUT Low Output Voltage               | V <sub>OL</sub>                | V <sub>CCD</sub> = 3V, I <sub>OL</sub> = 2.0mA        |              |     | 0.4                        | V     |

| FOUT Rise/Fall Time                   | t <sub>R</sub> /t <sub>F</sub> | (0.1 x V <sub>CCD</sub> ) - (0.9 x V <sub>CCD</sub> ) |              | 2   |                            | ns    |

| FOUT Duty Cycle                       | t <sub>D</sub>                 | 0.5 x V <sub>CCD</sub> (Note 5)                       | 45           |     | 55                         | %     |

#### AC ELECTRICAL CHARACTERISTICS—TCXO

$(V_{CC} = 3.135V \text{ to } 3.465V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 1)

| PARAM                               | METER                                            | SYMBOL            | CONDITIONS                     | MIN                      | TYP | MAX                      | UNITS |

|-------------------------------------|--------------------------------------------------|-------------------|--------------------------------|--------------------------|-----|--------------------------|-------|

| Frequency Stability vs. Temperature |                                                  | Δf/f <sub>C</sub> | CL = 10pF to ground            | f <sub>C</sub><br>– 1ppm | fC  | f <sub>C</sub><br>+ 1ppm | ppm   |

| Frequency Stabi                     | lity vs. Voltage                                 | ∆fvoltage<br>/fc  | CL = 10pF to ground, +25°C     | F to ground, +25°C -2 +2 |     | ppm/V                    |       |

| Aging                               | First Year                                       | Afranco /fa       | (Note 5)                       | -1                       |     | +1                       | nnm   |

| Aging                               | Years 2-20                                       | ∆faging/fc        | (Note 5)                       | -2                       |     | +2                       | ppm   |

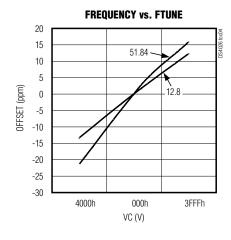

| Frequency Pull                      | Except 10MHz                                     | Δf/f <sub>C</sub> | FTUNEH = 3Fh and FTUNEL = FFh; | ±8                       | ±15 |                          | nnm   |

| Range                               | nge 10MHz FTUNEH = 40h and FTUNEL = 00h at +25°C |                   | ±5                             | ±10                      |     | ppm                      |       |

| Frequency Pull F                    | Resolution                                       | ΔfRES/fC          |                                |                          | 1   | ·                        | ppb   |

#### **AC ELECTRICAL CHARACTERISTICS—STRATUM 3**

(V<sub>CC</sub> = +3.135V to +3.465V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                                 | SYMBOL                                    | CONDITIONS                                                                                |       | TYP | MAX   | UNITS |

|-------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------|-------|-----|-------|-------|

| STRATUM 3 FREQUENCY STAB                  | LITY                                      |                                                                                           |       |     |       |       |

| Frequency Stability vs. Temperature       | Δf <sub>TEMP</sub> /f <sub>C</sub>        | -40°C to +85°C (Note 6)                                                                   | -0.28 |     | +0.28 | ppm   |

| Initial Tolerance and Reflow              | ΔfINITIAL /fC                             | T <sub>A</sub> = +25°C, ±3°C and V <sub>DD</sub> = 3.3V                                   | -0.8  |     | +0.8  | ppm   |

| Frequency Stability vs. Voltage           | Δfvoltage<br>/f <sub>C</sub>              | V <sub>CC</sub> = 3.3V ±5%, C <sub>L</sub> = 10pF to ground,<br>+25°C (Note 7)            |       |     | +0.33 | ppm   |

| Frequency Stability vs.<br>Aging/20 Years | ΔfAGING/fC                                | f <sub>C</sub> = Nominal (Note 8)                                                         | -3.0  |     | +3.0  | ppm   |

| Frequency Stability vs. Load<br>Change    | Δf <sub>LOAD</sub> /f <sub>C</sub>        | Load = 10pF ±5%, +25°C (Note 5)                                                           | -0.1  |     | +0.1  | ppm   |

| Free-Run Accuracy                         |                                           | Operating temperature, load, supply, and initial tolerance, aging (20 years) (Notes 5, 8) | -4.6  |     | +4.6  | ppm   |

| Holdover Stability (24 Hours)             | Δf <sub>24</sub> HOURS<br>/f <sub>C</sub> | 24-hour elapsed time (Notes 5, 9)                                                         | -0.32 |     | +0.32 | ppm   |

#### **PHASE NOISE**

|           | PHASE NOISE (dBc/Hz) (TYPICAL, +25°C, 3.3V) |        |         |         |         |         |         |  |  |  |  |

|-----------|---------------------------------------------|--------|---------|---------|---------|---------|---------|--|--|--|--|

|           | OFFSET (MHz)                                | 10Hz   | 100Hz   | 1kHz    | 10kHz   | 100kHz  | 1MHz    |  |  |  |  |

|           | 12.80                                       | -88.41 | -130.16 | -147.84 | -150.84 | -151.71 | -151.87 |  |  |  |  |

|           | 19.44                                       | -82.63 | -125.12 | -145.03 | -146.87 | -151.69 | -151.52 |  |  |  |  |

|           | 20.00                                       | -83.71 | -120.76 | -145.44 | -150.96 | -151.18 | -151.45 |  |  |  |  |

| CARRIER   | 38.88                                       | -79.01 | -120.06 | -141.75 | -150.59 | -152.50 | -153.06 |  |  |  |  |

| FREQUENCY | 40.00                                       | -80.80 | -115.44 | -141.17 | -151.59 | -152.37 | -153.00 |  |  |  |  |

|           | 51.84                                       | -74.09 | -120.39 | -142.33 | -151.14 | -153.21 | -153.94 |  |  |  |  |

|           | 10.0                                        | -92.52 | -134.83 | -147.22 | -150.84 | -151.25 | -150.84 |  |  |  |  |

|           | 16.384                                      | -87.44 | -128.53 | -147.67 | -150.78 | -152.72 | -151.75 |  |  |  |  |

|           | 16.8                                        | -89.6  | -126.20 | -146.88 | -151.90 | -152.28 | -151.93 |  |  |  |  |

|           | 24.0                                        | -83.98 | -119.45 | -143.08 | -150.33 | -150.34 | -150.67 |  |  |  |  |

#### TEMPERATURE SENSOR ELECTRICAL CHARACTERISTICS

$(V_{CC} = 3.135V \text{ to } 3.465V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                          | SYMBOL | CONDITIONS | MIN | TYP | MAX | UNITS |

|------------------------------------|--------|------------|-----|-----|-----|-------|

| Temperature Sensor Accuracy        | ΔΤ     |            | -3  |     | +3  | °C    |

| Temperature Sensor Conversion Time | tCONVT |            |     |     | 11  | ms    |

| Temperature Sensor Resolution      | N2     |            |     |     | 12  | Bits  |

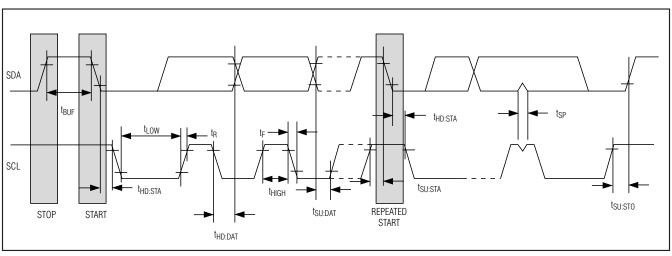

### AC ELECTRICAL CHARACTERISTICS—I<sup>2</sup>C SERIAL INTERFACE

(V<sub>CC</sub> = 3.135V to 3.465V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                         | SYMBOL           | CONDITIONS    | MIN TYP                | MAX  | UNITS |  |  |

|-----------------------------------|------------------|---------------|------------------------|------|-------|--|--|

| SCI Clock Fraguency               | foor             | Standard mode | 0                      | 100  | kHz   |  |  |

| SCL Clock Frequency               | fscl             | Fast mode     | 100                    | 400  | 7 KHZ |  |  |

| Bus Free Time Between STOP        | tour             | Standard mode | 4.7                    |      | 0     |  |  |

| and START Conditions              | t <sub>BUF</sub> | Fast mode     | 1.3                    |      | μs    |  |  |

| Hold Time (Repeated) START        | tup ota          | Standard mode | 4.0                    |      |       |  |  |

| Condition (Note 10)               | thd:Sta          | Fast mode     | 0.6                    |      | μs    |  |  |

| Low Period of SCL Clock           | tLOW             | Standard mode | 4.7                    |      | 110   |  |  |

| LOW FERIOR OF SCE CIOCK           | iLOW             | Fast mode     | 1.3                    |      | μs    |  |  |

| High Period of SCL Clock          | turou            | Standard mode | 4.0                    |      |       |  |  |

| Fight Fellod of SCL Clock         | thigh            | Fast mode     | 0.6                    |      | - µs  |  |  |

| Data Hold Time                    | thd:dat          | Standard mode | 0                      | 0.9  | μs    |  |  |

| (Notes 11, 12)                    | IND:DAT          | Fast mode     | 0                      | 0.9  | μο    |  |  |

| Data Setup Time (Note 13)         | tsu:DAT          | Standard mode | 250                    |      | ns    |  |  |

| Data Setup Time (Note 13)         |                  | Fast mode     | 100                    |      | 110   |  |  |

| START Setup Time                  | tsu:sta          | Standard mode | 4.7                    | 4.7  |       |  |  |

| START Setup Time                  | 150:51A          | Fast mode     | 0.6                    |      | μs    |  |  |

| Rise Time of Both SDA and SCL     | t <sub>R</sub>   | Standard mode | 20 + 0.1C <sub>B</sub> | 1000 | ns    |  |  |

| Signals (Note 14)                 | I IR             | Fast mode     | 20 + 0.1C <sub>B</sub> | 300  | 115   |  |  |

| Fall Time of Both SDA and SCL     | t⊨               | Standard mode | 20 + 0.1C <sub>B</sub> | 300  | ns    |  |  |

| Signals (Note 14)                 | 나                | Fast mode     | 20 + 0.1C <sub>B</sub> | 300  | 115   |  |  |

| Setup Time for STOP Condition     | touloto          | Standard mode | 4.7                    |      |       |  |  |

| Setup Time for STOF Condition     | tsu:sto          | Fast mode     | 0.6                    |      | — μs  |  |  |

| Pin Capacitance SDA, SCL (Note 5) | C <sub>I/O</sub> |               |                        | 10   | рF    |  |  |

### AC ELECTRICAL CHARACTERISTICS—I<sup>2</sup>C SERIAL INTERFACE (continued)

$(V_{CC} = 3.135 \text{V to } 3.465 \text{V}, T_A = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER                                                               | SYMBOL | CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------------------------------------------------------------|--------|------------|-----|-----|-----|-------|

| Capacitive Load for Each Bus<br>Line (Note 14)                          | Св     |            |     |     | 400 | рF    |

| Pulse Width of Spikes That Must<br>Be Suppressed by the Input<br>Filter | tsp    | Fast mode  |     | 30  |     | ns    |

- **Note 1:** Typical values are at +25°C, nominal supply voltages, unless otherwise indicated.

- Note 2: Voltages referenced to ground.

- **Note 3:** Limits at -40°C are guaranteed by design and not production tested.

- **Note 4:** Specified with I<sup>2</sup>C bus inactive.

- Note 5: Guaranteed by design and not production tested.

- **Note 6:** Frequency stability vs. temperature is defined as  $(\Delta f_{MAX} \Delta f_{MIN})/2$ .

- **Note 7:** Maximum power-supply variations to meet the specification are 5%.

- Note 8: Crystal vendor specification.

- Note 9: Holdover is defined as  $(f_{MAX} f_{MIN})/2$  as measured within a 24-hour period. Warmup time = 1 hour.

- **Note 10:** After this period, the first clock pulse is generated.

- Note 11: A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IH(MIN)</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 12: The maximum t<sub>HD:DAT</sub> need only be met if the device does not stretch the low period (t<sub>LOW</sub>) of the SCL signal.

- Note 13: A fast-mode device can be used in a standard-mode system, but the requirement that t<sub>SU:DAT</sub> ≥ 250ns must then be met. This is automatically the case if the device does not stretch the low period of the SCL signal. If such a device does not stretch the low period of the SCL signal, it must output the next data bit to the SDA line t<sub>R(MAX)</sub> + t<sub>SU:DAT</sub> = 1000 + 250 = 1250ns before the SCL line is released.

- Note 14: C<sub>R</sub>—total capacitance of one bus line in pF.

### Data Transfer on I<sup>2</sup>C Serial Bus

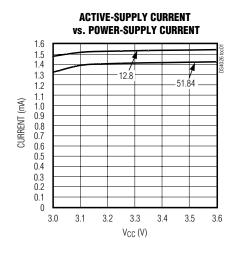

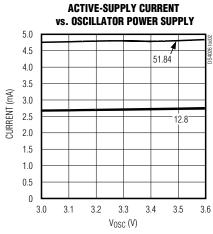

### Typical Operating Characteristics

( $V_{CC} = +3.3V$ ,  $T_A = +25$ °C, unless otherwise noted.)

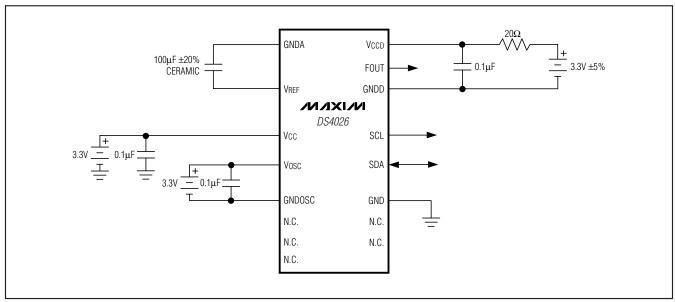

### **Pin Description**

| PIN  | NAME   | FUNCTION                                                                                                                                                                                                    |

|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | GNDA   | Ground for DAC                                                                                                                                                                                              |

| 2    | VREF   | Voltage Reference Output. This pin must be decoupled with a 100µF ceramic capacitor to ground.                                                                                                              |

| 3    | Vcc    | Power Supply for Digital Control and Temperature Sensor. This pin must be decoupled with a 100nF capacitor to ground.                                                                                       |

| 4    | Vosc   | Power Supply for Oscillator Circuit. This pin must be decoupled with a 0.1µF capacitor to ground.                                                                                                           |

| 5    | GNDOSC | Ground for Oscillator Circuit                                                                                                                                                                               |

| 6–10 | N.C.   | No Connection. Must be connected to ground.                                                                                                                                                                 |

| 11   | GND    | Ground for Digital Control, Temperature Sensor, and Controller Substrate                                                                                                                                    |

| 12   | SDA    | Serial Data Input/Output. SDA is the data input/output for the I <sup>2</sup> C interface. This open-drain pin requires an external pullup resistor.                                                        |

| 13   | SCL    | Serial Clock Input. SCL is the clock input for the I <sup>2</sup> C Interface and is used to synchronize data movement on the serial interface.                                                             |

| 14   | GNDD   | Ground for Oscillator Output Driver                                                                                                                                                                         |

| 15   | FOUT   | Frequency Output, CMOS Push-Pull                                                                                                                                                                            |

| 16   | VCCD   | Power Supply for Oscillator Output Driver. This pin must be decoupled with a $0.1\mu F$ capacitor to ground. A $20\Omega$ resistor must be placed in series between the power supply and V <sub>CCD</sub> . |

Figure 1. Typical Operating Circuit

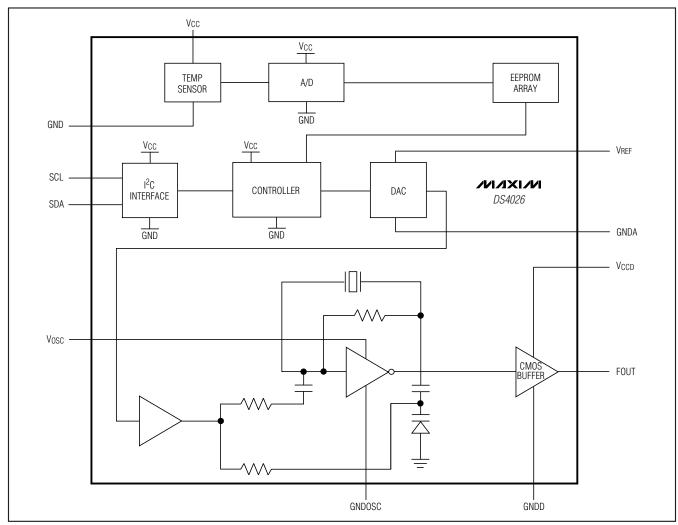

Figure 2. Functional Diagram

## **Detailed Description**

The DS4026 is a TCXO capable of operating at  $3.3V \pm 5\%$ , and it allows digital tuning of the fundamental frequency. The device is calibrated in the factory to achieve an accuracy of  $\pm 1$ ppm over the industrial temperature range, and its minimum pullability is  $\pm 8$ ppm with a typical resolution of 1ppb (typ) per LSB.

The DS4026 contains the following blocks:

- Oscillator block with variable capacitor for compensation

- Output driver block

- Temperature sensor

- Controller to read the temperature, control lookup table, and adjust the DAC input

- DAC output to adjust the capacitive load

- I<sup>2</sup>C interface to communicate with the chip

The oscillator block consists of an amplifier and variable capacitor in a Pierce crystal oscillator with a crystal resonator of fundamental mode. The oscillator amplifier is a single transistor amplifier and its transconductance is temperature compensated. The variable capacitor is adjusted by the DAC to provide temperature compensation. With the FTUNEH and FTUNEL registers, a minimum pullability of ±8ppm (±5ppm for 10MHz) is achieved with a typical resolution of 1ppb (typ) per LSB.

NIXI/N

The output driver is a CMOS square-wave output with symmetrical rise and fall time.

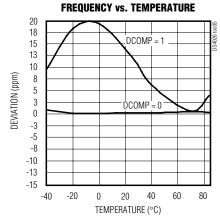

The temperature sensor provides a 12-bit temperature reading with a resolution of 0.0625°C. The sensor is in continuous conversion mode. If DCOMP is set, conversions continue but temperature updates are inhibited.

The controller coordinates the conversion of temperature into digital codes. When the temperature reading is different from the previous one or the frequency tuning register is changed, the controller looks up the two corresponding capacitance trim codes from the lookup table at a 0.5°C increment. The trim codes are interpolated to 0.0625°C resolution.

The result is added with the tuning value from the frequency tuning register and loaded into the DAC registers to adjust voltage output. The monotonic DAC provides an analog voltage based on temperature compensation to drive the variable capacitor.

The DS4026 operates as a slave device on the serial bus. Access is obtained by implementing a START condition and providing a device identification code followed by data. Subsequent registers can be accessed sequentially until a STOP condition is executed.

### Address Map

#### **Disable Compensation Update (DCOMP)**

DCOMP is bit 7 of the frequency tuning register (see the *Frequency Tuning Register (00h–01h), POR = 00h* table). When set to logic 1, this bit's temperature-compensation function is disabled. This disabling prevents the variable capacitor in the oscillator block from changing. However, the temperature register still performs temperature conversions. The temperature trim code from the last temperature conversion before DCOMP is enabled is used for temperature compensation. The FTUNE registers are still functional when DCOMP is disabled.

The frequency tuning registers adjust the base frequency. The frequency tuning value is represented in two's complement data. Bit 6 of FTUNEH is the sign, bit 5 is the MSB, and bit 0 of FTUNEL is the LSB (see Table 1). When the tuning register low (01h) is programmed with a value, the next temperature update cycle sums the programmed value with the factory compensated value. This allows the user to digitally control the base frequency using the I<sup>2</sup>C protocol.

These frequency tuning register bits allow the tuning of the base frequency. Each bit typically represents about 1ppb (typ). For FTUNEH = 3Fh and FTUNEL = FFh, the device pushes the base frequency by approximately +15ppm.

#### Frequency Tuning Register (00h-01h), POR = 00h

| ADDRESS | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| 00h     | DCOMP | Sign  | Data  | Data  | Data  | Data  | Data  | Data  |

| POR     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 01h     | Data  |

| POR     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### Temperature Register (02h-03h)

| ADDRESS | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| 02h     | Sign  | Data  |

| POR     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 03h     | Data  | Data  | Data  | Data  | 0     | 0     | 0     | 0     |

| POR     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### Table 1. Register Map

| ADDRESS | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3  | BIT 2 | BIT 1 | BIT 0 | FUNCTION              |

|---------|-------|-------|-------|-------|--------|-------|-------|-------|-----------------------|

| 00      | DCOMP | SIGN  |       |       | FTUNEH |       |       |       | Frequency Tuning High |

| 01      |       |       |       |       | FTUNEL |       |       |       | Frequency Tuning Low  |

| 02      | SIGN  |       |       |       | TREGH  |       |       |       | Temperature MSB       |

| 03      |       | -     |       | -     | TREGL  |       |       |       | Temperature LSB       |

#### **Read Mode**

In the temperature register (see the *Temperature Register (02h–03h)* table), temperature is represented as a 12-bit code and is accessible at location 02h and 03h. The upper 8 bits are at location 02h and the lower 4 bits are in the upper nibble of the byte at location 03h. Upon power reset, the registers are set to a +25°C default temperature and the controller starts a temperature conversion. The temperature register stores new temperature readings.

The current temperature is loaded into the (user) temperature registers when a valid I<sup>2</sup>C slave address and write is received and when a word address is received. Consequently, if the two temperature registers are read in individual I<sup>2</sup>C transactions, it is possible for a temperature conversion to occur between reads, and the results can be inaccurate. To prevent this from occurring, the registers should be read using a single, multibyte read operation (Figure 5). I<sup>2</sup>C reads do not affect the internal temperature registers.

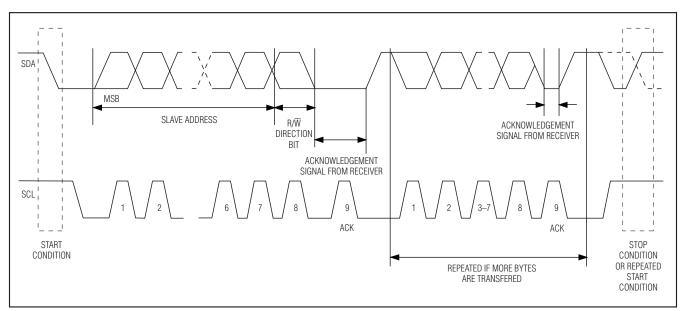

### I<sup>2</sup>C Serial Data Bus

The DS4026 supports a bidirectional I<sup>2</sup>C bus and data transmission protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data is defined as a receiver. The device that controls the message is called a master. The devices that are controlled by the master are slaves. The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions. The DS4026 operates as a slave on the I<sup>2</sup>C bus. Connections to the bus are made through the open-drain I/O lines SDA and SCL. Within the bus specifications, a standard mode (100kHz maximum clock rate) and a fast mode (400kHz maximum clock rate) are defined. The DS4026 works in both modes.

The following bus protocol has been defined (Figure 3):

Data transfer can be initiated only when the bus is not busy.

Figure 3. I<sup>2</sup>C Data Transfer Overview

10

MIXI/N \_\_\_\_\_\_

During data transfer, the data line must remain stable whenever the clock line is high. Changes in the data line while the clock line is high are interpreted as control signals.

Accordingly, the following bus conditions have been defined:

**Bus not busy:** Both data and clock lines remain high.

**START data transfer:** A change in the state of the data line from high to low, while the clock line is high, defines a START condition.

**STOP data transfer:** A change in the state of the data line from low to high, while the clock line is high, defines a STOP condition.

**Data valid:** The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the high period of the clock signal. The data on the line must be changed during the low period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between the START and the STOP conditions is not limited, and is determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit.

**Acknowledge:** Each receiving device, when addressed, is obliged to generate an acknowledge (ACK) after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit.

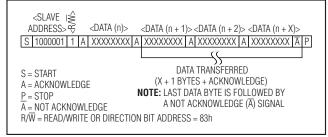

Figure 4. Slave Receiver Mode (Write Mode)

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable low during the high period of the acknowledge-related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line high to enable the master to generate the STOP condition.

Figures 4 and 5 detail how data transfer is accomplished on the  $I^2C$  bus. Depending upon the state of the  $R\overline{W}$  bit, two types of data transfer are possible:

**Data transfer from a master transmitter to a slave receiver.** The first byte transmitted by the master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge (ACK) bit after each received byte.

Data transfer from a slave transmitter to a master receiver. The first byte (the slave address) is transmitted by the master. The slave then returns an acknowledge bit. Next follows a number of data bytes transmitted by the slave to the master. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a not acknowledge (NACK) is returned.

The master device generates all the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Because a repeated START condition is also the beginning of the next serial transfer, the bus is not released.

Figure 5. Slave Transmitter Mode (Read Mode)

The DS4026 can operate in the following two modes:

Slave receiver mode (write mode): Serial data and clock are received through SDA and SCL. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit. The slave address byte is the first byte received after the master generates a START condition. The slave address byte contains the 7-bit DS4026 address, which is 1000001, followed by the direction bit  $(R/\overline{W})$ , which is 0 for a write. After receiving and decoding the slave address byte, the DS4026 outputs an acknowledge on SDA. After the DS4026 acknowledges the slave address and write bit, the master transmits a word address to the DS4026. This sets the register pointer on the DS4026, with the DS4026 acknowledging the transfer. The master can then transmit zero or more bytes of data, with the DS4026 acknowledging each byte received. The register pointer increments after each data byte is transferred. The master generates a STOP condition to terminate the data write.

Slave transmitter mode (read mode): The first byte is received and handled as in the slave receiver mode. However, in this mode, the direction bit indicates that the transfer direction is reversed. Serial data is transmitted on SDA by the DS4026 while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit. The slave address byte is the first byte received after the master generates a START condition. The slave address byte contains the 7-bit DS4026 address, which is 1000001, followed by the direction bit (R/W), which is 1 for a read. After receiving and decoding the slave address byte, the DS4026 outputs an acknowledge on SDA. The DS4026 then begins to transmit data starting with the register address pointed to by the register pointer. If the register pointer is not written to before the initiation of a read mode, the first address that is read is the last one stored in the register pointer. The DS4026 must receive a not acknowledge to end a read.

### Ordering Information (continued)

| PART        | TEMP RANGE     | OUTPUT (f <sub>C</sub> )<br>(MHz, CMOS) | PIN-PACKAGE | TOP MARK*  |

|-------------|----------------|-----------------------------------------|-------------|------------|

| DS4026S+HCC | 0°C to +70°C   | 19.44                                   | 16 SO       | DS4026-HCC |

| DS4026S+HCN | -40°C to +85°C | 19.44                                   | 16 SO       | DS4026-HCN |

| DS4026S+JCC | 0°C to +70°C   | 20.00                                   | 16 SO       | DS4026-JCC |

| DS4026S+JCN | -40°C to +85°C | 20.00                                   | 16 SO       | DS4026-JCN |

| DS4026S+MCC | 0°C to +70°C   | 38.88                                   | 16 SO       | DS4026-MCC |

| DS4026S+MCN | -40°C to +85°C | 38.88                                   | 16 SO       | DS4026-MCN |

| DS4026S+PCC | 0°C to +70°C   | 40.00                                   | 16 SO       | DS4026-PCC |

| DS4026S+PCN | -40°C to +85°C | 40.00                                   | 16 SO       | DS4026-PCN |

| DS4026S+QCC | 0°C to +70°C   | 51.84                                   | 16 SO       | DS4026-QCC |

| DS4026S+QCN | -40°C to +85°C | 51.84                                   | 16 SO       | DS4026-QCN |

| DS4026S+RCC | 0°C to +70°C   | 24.00                                   | 16 SO       | DS4026-RCC |

| DS4026S+RCN | -40°C to +85°C | 24.00                                   | 16 SO       | DS4026-RCN |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

# Ordering Information—Stratum 3

| PART         | TEMP RANGE     | OUTPUT (f <sub>C</sub> )<br>(MHz, CMOS) | PIN-PACKAGE | TOP MARK*    |

|--------------|----------------|-----------------------------------------|-------------|--------------|

| DS4026S3+ACN | -40°C to +85°C | 10.00                                   | 16 SO       | DS4026S3-ACN |

| DS4026S3+BCN | -40°C to +85°C | 12.80                                   | 16 SO       | DS4026S3-BCN |

| DS4026S3+GCN | -40°C to +85°C | 19.20                                   | 16 SO       | DS4026S3-GCN |

| DS4026S3+JCN | -40°C to +85°C | 20.00                                   | 16 SO       | DS4026S3-JCN |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

### **Chip Information**

TRANSISTOR COUNT: 77, 712

SUBSTRATE CONNECTED TO GROUND

PROCESS: CMOS

# Package Information

For the latest package outline information and land patterns, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.

| PACKAGE TYPE     | PACKAGE CODE | DOCUMENT NO. |

|------------------|--------------|--------------|

| 16 SO (300 mils) | W16+H1       | 21-0042      |

<sup>\*</sup>The top mark will include a "+" for a lead(Pb)-free/RoHS-compliant device.

<sup>\*</sup>The top mark will include a "+" for a lead(Pb)-free/RoHS-compliant device.

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                                                                                                                                                                                                                                                | PAGES<br>CHANGED |

|--------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 2/07          | Initial release.                                                                                                                                                                                                                                                                                           | _                |

| 1                  | 9/07          | Changed device from 12.8MHz to 51.84MHz to 10MHz to 51.84MHz; added ±5ppm (min, typ) digital frequency tuning for the 10MHz option; added new ordering information and phase noise data; changed capacitor value designators from 10nF to 0.1µF; changed push-pull value from ±15ppm (typ) to ±8ppm (min). | 1–12             |

| 2                  | 4/08          | Changed maximum frequency deviation from over 10 years to over 20 years;<br>Added Stratum 3 electrical characteristics table; added ordering information for<br>Stratum 3 parts.                                                                                                                           | 1, 5, 13         |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### О компании

ООО "ТрейдЭлектроникс" - это оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов. Реализуемая нашей компанией продукция насчитывает более полумиллиона наименований.

Благодаря этому наша компания предлагает к поставке практически не ограниченный ассортимент компонентов как оптовыми, мелкооптовыми партиями, так и в розницу.

Наличие собственной эффективной системы логистики обеспечивает надежную поставку продукции по конкурентным ценам в точно указанные сроки.

Срок поставки со стоков в Европе и Америке – от 3 до 14 дней.

Срок поставки из Азии - от 10 дней.

Благодаря развитой сети поставщиков, помогаем в поиске и приобретении экзотичных или снятых с производства компонентов.

Предоставляем спец цены на элементы для создания инженерных сэмплов.

Упорный труд, качественный результат дают нам право быть уверенными в себе и надежными для наших клиентов.

#### Наша компания это:

- Гарантия качества поставляемой продукции

- Широкий ассортимент

- Минимальные сроки поставок

- Техническая поддержка

- Подбор комплектации

- Индивидуальный подход

- Гибкое ценообразование

Наша организация особенно сильна в поставках модулей, микросхем, пассивных компонентов, ксайленсах (XC), EPF, EPM и силовой электроники.

Большой выбор предлагаемой продукции, различные виды оплаты и доставки, позволят Вам сэкономить время и получить максимум выгоды от сотрудничества с нами!

## <u>Перечень производителей, продукцию которых мы поставляем</u> на российский рынок

**Panasonic**

RENESAS

**SIEMENS**

гарантия бесперебойности производства и качества выпускаемой продукции

С удовольствием будем прорабатывать для Вас поставки всех необходимых компонентов по текущим запросам для скорейшего выявления групп элементов, по которым сотрудничество именно с нашей компанией будет для Вас максимально выгодным!

С уважением,

Менеджер отдела продаж ООО

«Трейд Электроникс»

Шишлаков Евгений

8 (495)668-30-28 доб 169

manager28@tradeelectronics.ru

http://www.tradeelectronics.ru/