# 14-Bit 128 kSPS Complete Sampling ADC

AD679

#### **FEATURES**

AC and DC Characterized and Specified (K, B, T Grades)

128k Conversions per Second

1 MHz Full Power Bandwidth

500 kHz Full Linear Bandwidth

78 dB S/N+D (K, B, T Grades)

Twos Complement Data Format (Bipolar Mode)

Straight Binary Data Format (Unipolar Mode)

10 MΩ Input Impedance

8-Bit Bus Interface

On-Board Reference and Clock

10 V Unipolar or Bipolar Input Range

Pin Compatible with AD678 12-Bit, 200 kSPS ADC

MIL-STD-883 Compliant Versions Available

#### **GENERAL DESCRIPTION**

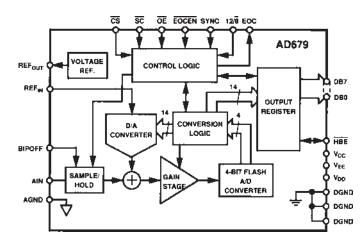

The AD679 is a complete, multipurpose 14-bit monolithic analog-to-digital converter, consisting of a sample-and-hold amplifier (SHA), a microprocessor-compatible bus interface, a voltage reference, and clock generation circuitry.

The AD679 is specified for ac (or dynamic) parameters such as S/N+D ratio, THD, and IMD, which are important in signal processing applications. In addition, the AD679K, B, and T grades are fully specified for dc parameters that are important in measurement applications.

The 14 data bits are accessed in two read operations (8 + 6), with left justification. Data format is straight binary for unipolar mode and twos complement binary for bipolar mode. The input has a full-scale range of 10 V with a full power bandwidth of 1 MHz and a full linear bandwidth of 500 kHz. High input impedance (10 M $\Omega$ ) allows direct connection to unbuffered sources without signal degradation. Conversions can be initiated either under microprocessor control or by an external clock asynchronous to the system clock.

This product is fabricated on Analog Devices' BiMOS process, combining low power CMOS logic with high precision, low noise bipolar circuits; laser-trimmed thin-film resistors provide high accuracy. The converter utilizes a recursive subranging algorithm that includes error correction and flash converter circuitry to achieve high speed and resolution.

The AD679 operates from +5 V and  $\pm 12$  V supplies and dissipates 560 mW (typ). The part is available in 28-lead plastic DIP, ceramic DIP, and 44 J-leaded ceramic surface-mount packages.

#### REV. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

#### FUNCTIONAL BLOCK DIAGRAM

#### PRODUCT HIGHLIGHTS

- 1. COMPLETE INTEGRATION: The AD679 minimizes external component requirements by combining a high speed sample-and-hold amplifier (SHA), ADC, 5 V reference, clock, and digital interface on a single chip. This provides a fully specified sampling A/D function unattainable with discrete designs.

- 2. SPECIFICATIONS: The AD679K, B, and T grades provide fully specified and tested ac and dc parameters. The AD679J, A, and S grades are specified and tested for ac parameters; dc accuracy specifications are shown as typicals. DC specifications (such as INL, gain, and offset) are important in control and measurement applications. AC specifications (such as S/N+D ratio, THD, and IMD) are of value in signal processing applications.

- 3. EASE OF USE: The pinout is designed for easy board layout, and the two-read output provides compatibility with 8-bit buses. Factory trimming eliminates the need for calibration modes or external trimming to achieve rated performance.

- 4. RELIABILITY: The AD679 utilizes Analog Devices' monolithic BiMOS technology. This ensures long-term reliability compared to multichip and hybrid designs.

- 5. UPGRADE PATH: The AD679 provides the same pinout as the 12-bit, 200 kSPS AD678 ADC.

- The AD679 is available in versions compliant with MIL-STD-883. Refer to the Analog Devices Military Products Databook or current AD679/883B data sheet for detailed specifications.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2004 Analog Devices, Inc. All rights reserved.

## AD679—SPECIFICATIONS

AC SPECIFICATIONS  $(T_{MIN}$  to  $T_{MAX}$ ,  $V_{CC} = +12$  V  $\pm$  5%,  $V_{EE} = -12$  V  $\pm$  5%,  $V_{DD} = +5$  V  $\pm$  10%,  $f_{SAMPLE} = 128$  kSPS,  $f_{IN} = 10.009$  kHz, unless otherwise noted)<sup>1</sup>

| 1                                                         |     | AD679J/A/S |       |     | AD679K/B/T |       |      |

|-----------------------------------------------------------|-----|------------|-------|-----|------------|-------|------|

| Parameter                                                 | Min | Typ        | Max   | Min | Typ        | Max   | Unit |

| SIGNAL-TO-NOISE AND DISTORTION (S/N+D) RATIO <sup>2</sup> |     |            |       |     |            |       |      |

| −0.5 dB Input (Referred to −0 dB Input)                   | 76  | 79         |       | 78  | 81         |       | dB   |

| −20 dB Input (Referred to −20 dB Input)                   | 58  | 59         |       | 60  | 61         |       | dB   |

| -60 dB Input (Referred to -60 dB Input)                   | 18  | 19         |       | 20  | 21         |       | dB   |

| TOTAL HARMONIC DISTORTION (THD) <sup>3</sup>              |     |            |       |     |            |       |      |

| @ 25°C                                                    |     | -90        | -82   |     | -90        | -82   | dB   |

|                                                           |     | 0.003      | 0.006 |     | 0.003      | 0.006 | %    |

| $\mathrm{T_{MIN}}$ to $\mathrm{T_{MAX}}$                  |     | -88        | -82   |     | -88        | -82   | dB   |

|                                                           |     | 0.004      | 0.008 |     | 0.004      | 0.008 | %    |

| PEAK SPURIOUS OR PEAK HARMONIC COMPONENT                  |     | -90        | -82   |     | -90        | -82   | dB   |

| FULL POWER BANDWIDTH                                      |     | 1          |       |     | 1          |       | MHz  |

| FULL LINEAR BANDWIDTH                                     | 500 |            |       | 500 |            |       | kHz  |

| INTERMODULATION DISTORTION (IMD) <sup>4</sup>             |     |            |       |     |            |       |      |

| 2nd Order Products                                        |     | -90        | -82   |     | -90        | -82   | dB   |

| 3rd Order Products                                        |     | -90        | -82   |     | -90        | -82   | dB   |

#### NOTES

Specifications subject to change without notice.

## **DIGITAL SPECIFICATIONS** (All device types $T_{MIN}$ to $T_{MAX}$ , $V_{CC} = +12$ V $\pm$ 5%, $V_{EE} = -12$ V $\pm$ 5%, $V_{DD} = +5$ V $\pm$ 10%)

| Parameter                          |                           | <b>Test Conditions</b>               | Min | Max         | Unit |

|------------------------------------|---------------------------|--------------------------------------|-----|-------------|------|

| LOGIC IN                           | NPUTS                     |                                      |     |             |      |

| $ m V_{IH}$                        | High Level Input Voltage  |                                      | 2.0 | $ m V_{DD}$ | V    |

| $ m V_{IL}$                        | Low Level Input Voltage   |                                      | 0   | 0.8         | V    |

| ${ m I}_{ m IH}$                   | High Level Input Current  | $V_{IN} = 5 \text{ V}$               | -10 | +10         | μΑ   |

|                                    | Low Level Input Current   | $V_{IN} = 0 V$                       | -10 | +10         | μΑ   |

| I <sub>IL</sub><br>C <sub>IN</sub> | Input Capacitance         |                                      |     | 10          | pF   |

| LOGIC O                            | UTPUTS                    |                                      |     |             |      |

| $V_{OH}$                           | High Level Output Voltage | $I_{OH} = 0.1 \text{ mA}$            | 4.0 |             | V    |

|                                    |                           | $I_{OH} = 0.5 \text{ mA}$            | 2.4 |             | V    |

| $V_{OL}$                           | Low Level Output Voltage  | $I_{OL} = 1.6 \text{ mA}$            |     | 0.4         | V    |

| $I_{OZ}$                           | High Z Leakage Current    | $V_{IN} = 0 \text{ or } 5 \text{ V}$ | -10 | +10         | μA   |

| $C_{OZ}$                           | High Z Output Capacitance |                                      |     | 10          | pF   |

#### NOTES

Specifications subject to change without notice.

-2- REV. D

¹f<sub>IN</sub> amplitude = −0.5 dB (9.44 V p-p) bipolar mode full scale unless otherwise indicated. All measurements referred to a −0 dB (9.997 V p-p) input signal unless otherwise noted.

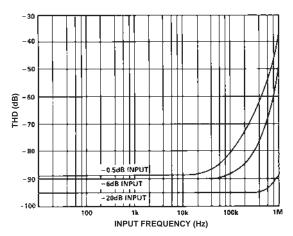

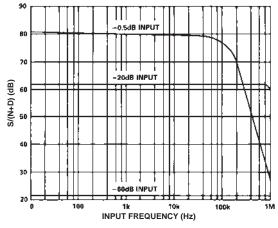

<sup>&</sup>lt;sup>2</sup>See TPC 3 for higher frequencies and other input amplitudes.

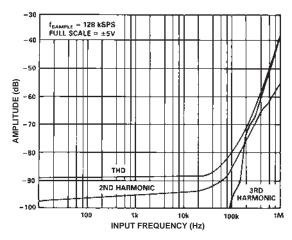

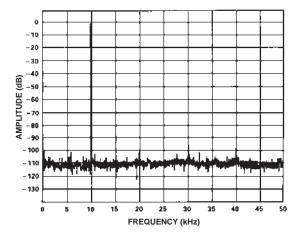

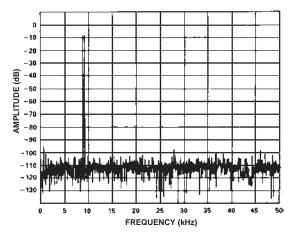

<sup>&</sup>lt;sup>3</sup>See TPCs 1 and 2 for higher frequencies and other input amplitudes.

$<sup>{}^{4}</sup>f_{A}$  = 9.08 kHz,  $f_{B}$  = 9.58 kHz, with  $f_{SAMPLE}$  100 kSPS. See Definition of Specifications section.

<sup>&</sup>lt;sup>1</sup>f<sub>IN</sub> amplitude = -0.5 dB (9.44 V p-p) bipolar mode full scale unless otherwise indicated. All measurements referred to a -0 dB (9.997 V p-p) input signal unless otherwise noted.

<sup>&</sup>lt;sup>2</sup>See TPC 3 for higher frequencies and other input amplitudes.

<sup>&</sup>lt;sup>3</sup>See TPCs 1 and 2 for higher frequencies and other input amplitudes.

$<sup>^4</sup>f_A$  = 9.08 kHz,  $f_B$  = 9.58 kHz, with  $f_{SAMPLE}$  100 kSPS. See Definition of Specifications section.

**DC SPECIFICATIONS** ( $T_{MIN}$  to  $T_{MAX}$ ,  $V_{CC} = +12$  V  $\pm$  5%,  $V_{EE} = -12$  V  $\pm$  5%,  $V_{DD} = +5$  V  $\pm$  10%, unless otherwise noted)

| AD679J/A/S                                |            |            |      | AD679K/B/T |      |           |                    |  |

|-------------------------------------------|------------|------------|------|------------|------|-----------|--------------------|--|

| Parameter                                 | Min        | Тур        | Max  | Min        | Тур  | Max       | Unit               |  |

| ΓEMPERATURE RANGE                         |            |            |      |            |      |           |                    |  |

| J, K Grades                               | 0          |            | 70   | 0          |      | 70        | °C                 |  |

| A, B Grades                               | -40        |            | +85  | -40        |      | +85       | °C                 |  |

| S, T Grades                               | -55        |            | +125 | -55        |      | +125      | °C                 |  |

|                                           | -55        |            | T123 | -55        |      | T125      | C                  |  |

| ACCURACY                                  |            |            |      |            |      |           | D:                 |  |

| Resolution                                | 14         |            |      | 14         |      |           | Bits               |  |

| Integral Nonlinearity (INL)               |            | <b>±</b> 2 |      |            | ±1   | $\pm 2.5$ | LSB                |  |

| Differential Nonlinearity (DNL)           | 14         |            |      | 14         |      |           | Bits               |  |

| Unipolar Zero Error <sup>1</sup> (@ 25°C) |            | 0.08       |      |            | 0.05 | 0.07      | % FSR <sup>2</sup> |  |

| Bipolar Zero Error <sup>1</sup> (@ 25°C)  |            | 0.08       |      |            | 0.05 | 0.07      | % FSR              |  |

| Gain Error <sup>1, 3</sup> (@ 25°C)       |            | 0.12       |      |            | 0.09 | 0.11      | % FSR              |  |

| Temperature Drift                         |            |            |      |            |      |           |                    |  |

| Unipolar Zero <sup>4</sup>                |            |            |      |            |      |           |                    |  |

| J, K Grades                               |            | 0.04       |      |            | 0.04 | 0.05      | % FSR              |  |

| A, B Grades                               |            | 0.05       |      |            | 0.05 | 0.07      | % FSR              |  |

| S, T Grades                               |            | 0.09       |      |            | 0.09 | 0.10      | % FSR              |  |

| Bipolar Zero <sup>4</sup>                 |            | 0.09       |      |            | 0.09 | 0.10      | /0 I OIC           |  |

| J, K Grades                               |            | 0.02       |      |            | 0.02 | 0.04      | % FSR              |  |

|                                           |            | 0.02       |      |            | 0.02 | 0.04      | % FSR<br>% FSR     |  |

| A, B Grades                               |            |            |      |            |      |           |                    |  |

| S, T Grades                               |            | 0.08       |      |            | 0.08 | 0.09      | % FSR              |  |

| Gain <sup>4</sup>                         |            |            |      |            |      |           |                    |  |

| J, K Grades                               |            | 0.09       |      |            | 0.09 | 0.11      | % FSR              |  |

| A, B Grades                               |            | 0.10       |      |            | 0.10 | 0.16      | % FSR              |  |

| S, T Grades                               |            | 0.20       |      |            | 0.20 | 0.25      | % FSR              |  |

| Gain⁵                                     |            |            |      |            |      |           |                    |  |

| J, K Grades                               |            | 0.04       |      |            | 0.04 | 0.05      | % FSR              |  |

| A, B Grades                               |            | 0.05       |      |            | 0.05 | 0.07      | % FSR              |  |

| S, T Grades                               |            | 0.09       |      |            | 0.09 | 0.10      | % FSR              |  |

| ANALOG INPUT                              |            |            |      |            |      |           |                    |  |

| Input Ranges                              |            |            |      |            |      |           |                    |  |

| Unipolar Mode                             | 0          |            | +10  | 0          |      | +10       | V                  |  |

| Bipolar Mode                              | <b>-</b> 5 |            | +5   | <b>-</b> 5 |      | +5        | V                  |  |

| Input Resistance                          | -3         | 10         | 13   | -3         | 10   | 13        | $M\Omega$          |  |

|                                           |            |            |      |            |      |           |                    |  |

| Input Capacitance                         |            | 10         | 1.5  |            | 10   | 1.5       | pF                 |  |

| Input Settling Time                       |            |            | 1.5  |            | 4.0  | 1.5       | μs                 |  |

| Aperture Delay                            |            | 10         |      |            | 10   |           | ns                 |  |

| Aperture Jitter                           |            | 150        |      |            | 150  |           | ps                 |  |

| INTERNAL VOLTAGE REFERENCE                |            |            |      |            |      |           |                    |  |

| Output Voltage <sup>6</sup>               | 4.98       |            | 5.02 | 4.98       |      | 5.02      | V                  |  |

| External Load                             |            |            |      |            |      |           |                    |  |

| Unipolar Mode                             |            |            | 1.5  |            |      | 1.5       | mA                 |  |

| Bipolar Mode                              |            |            | 0.5  |            |      | 0.5       | mA                 |  |

|                                           |            |            |      |            |      |           | <del>-</del>       |  |

| POWER SUPPLIES                            |            |            |      |            |      |           |                    |  |

| Power Supply Rejection                    |            |            |      |            |      |           | 1.05               |  |

| $V_{CC} = +12 V \pm 5\%$                  |            | ±6         |      |            |      | ±6        | LSB                |  |

| $V_{EE} = -12 \text{ V} \pm 5\%$          |            | ±6         |      |            |      | ±6        | LSB                |  |

| $V_{DD}$ = +5 V ± 10%                     |            | <b>±</b> 6 |      |            |      | ±6        | LSB                |  |

| Operating Current                         |            |            |      |            |      |           |                    |  |

| $I_{CC}$                                  |            | 18         | 20   |            | 18   | 20        | mA                 |  |

| $ m I_{EE}$                               |            | 25         | 34   |            | 25   | 34        | mA                 |  |

| $I_{\mathrm{DD}}$                         |            | 8          | 12   |            | 8    | 12        | mA                 |  |

| Power Consumption                         |            | 560        | 745  |            | 560  | 745       | mW                 |  |

|                                           |            |            |      |            |      |           |                    |  |

NOTES

Specifications subject to change without notice.

REV. D \_3\_

<sup>&</sup>lt;sup>1</sup>Adjustable to zero. See Figures 5 and 6.

<sup>&</sup>lt;sup>2</sup>% FSR = percent of full-scale range.

<sup>&</sup>lt;sup>3</sup>Includes internal voltage reference error.

<sup>&</sup>lt;sup>4</sup>Includes internal voltage reference drift.

<sup>&</sup>lt;sup>5</sup>Excludes internal voltage reference drift.

<sup>&</sup>lt;sup>6</sup>With maximum external load applied.

Specifications shown in **boldface** are tested on all devices at final electrical test with worst case supply voltages at  $T_{MIN}$ , 25°C and  $T_{MAX}$ . Results from those tests are used to calculate outgoing quality levels. All min and max specifications are guaranteed, although only those shown in **boldface** are tested.

# TIMING SPECIFICATIONS (All device types $T_{MIN}$ to $T_{MAX}$ , $V_{CC}=+12$ V $\pm$ 5%, $V_{EE}=-12$ V $\pm$ 5%, $V_{DD}=+5$ V $\pm$ 10%)

| Parameter                    | Symbol            | Min   | Max             | Unit |

|------------------------------|-------------------|-------|-----------------|------|

| SC Delay                     | t <sub>SC</sub>   | 50    |                 | ns   |

| Conversion Time              | t <sub>C</sub>    |       | 6.3             | μs   |

| Conversion Rate <sup>1</sup> | t <sub>CR</sub>   |       | 7.8             | μs   |

| Convert Pulse Width          | $t_{CP}$          | 0.097 | 3.0             | μs   |

| Aperture Delay               | $t_{ m AD}$       | 5     | 20              | ns   |

| Status Delay                 | $t_{\mathrm{SD}}$ | 0     | 400             | ns   |

| Access Time <sup>2, 3</sup>  | $t_{BA}$          | 10    | 100             | ns   |

|                              |                   | 10    | 57 <sup>4</sup> | ns   |

| Float Delay <sup>5</sup>     | $t_{ m FD}$       | 10    | 80              | ns   |

| Output Delay                 | t <sub>OD</sub>   |       | 0               | ns   |

| Format Setup                 | $t_{\mathrm{FS}}$ | 100   |                 | ns   |

| OE Delay                     | t <sub>OE</sub>   | 20    |                 | ns   |

| Read Pulse Width             | t <sub>RP</sub>   | 195   |                 | ns   |

| Conversion Delay             | $t_{CD}$          | 400   |                 | ns   |

| EOCEN Delay                  | $t_{\rm EO}$      | 50    |                 | ns   |

#### NOTES

Specifications subject to change without notice.

NOTES  $^{1}\text{IN}$  ASYNCHRONOUS MODE, STATE OF  $\overline{\text{CS}}$  does not affect operation. SEE THE START CONVERSION TRUTH TABLE FOR DETAILS.

2EOCEN = LOW (SEE FIGURE 3). IN SYNCHRONOUS MODE, EOC IS A THREE-STATE OUTPUT. IN ASYNCHRONOUS MODE, EOC IS AN OPEN DRAIN OUTPUT. 3DATA SHOULD NOT BE ENABLED DURING A CONVERSION.

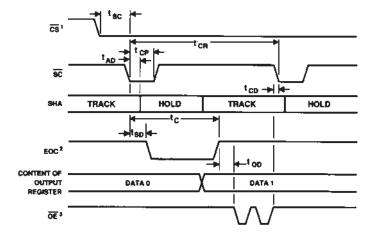

Figure 1. Conversion Timing

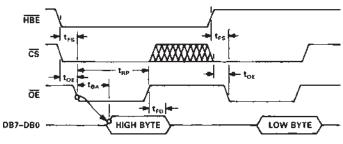

Figure 2. Output Timing

#### NOTE 1EOC IS A THREE-STATE OUTPUT IN SYNCHRONOUS MODE AND AN OPEN DRAIN OUTPUT IN ASYNCHRONOUS. ACCESS (tBA) AND FLOAT ( $t_{\mbox{\scriptsize FD}}$ ) TIMING SPECIFICATIONS DO NOT APPLY IN ASYNCHRONOUS MODE WHERE THEY ARE A FUNCTION OF THE TIME CONSTANT FORMED BY THE 10pF OUTPUT CAPACITANCE

AND THE PULL-UP RESISTOR.

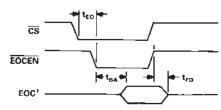

Figure 3. EOC Timing

| TEST                              | V <sub>CP</sub> | C <sub>OUT</sub> |

|-----------------------------------|-----------------|------------------|

| ACCESS TIME HIGH Z TO LOGIC LOW5V | 100pF           | T                |

| FLOAT TIME LOGIC HIGH TO HIGH Z   | 0V              | 10pF             |

| ACCESS TIME HIGH Z TO LOGIC HIGH  | 0V              | 100pF            |

| FLOAT TIME LOGIC LOW TO HIGH Z    | 5V              | 10pF             |

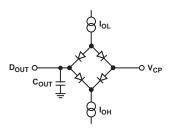

Figure 4. Load Circuit for Bus Timing Specifications

REV. D \_4\_

<sup>&</sup>lt;sup>1</sup>Includes acquisition time.

$<sup>^2</sup>$ Measured from the falling edge of  $\overline{OE}/\overline{EOCEN}$  (0.8 V) to the time at which the

data lines/EOC cross 2.0 V or 0.8 V. See Figure 4.

$<sup>{}^{3}</sup>C_{OUT} = 100 \text{ pF}.$

$<sup>{}^{4}</sup>C_{OUT} = 50 \text{ pF}.$

<sup>&</sup>lt;sup>5</sup>Measured from the rising edge of  $\overline{\text{OE}/\text{EOCEN}}$  (2.0 V) to the time at which the output voltage changes by 0.5. See Figure 4; C<sub>OUT</sub> = 10 pF.

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Specification          | With<br>Respect<br>To | Min      | Max                | Unit |

|------------------------|-----------------------|----------|--------------------|------|

| $V_{CC}$               | AGND                  | -0.3     | +18                | V    |

| $V_{EE}$               | AGND                  | -18      | +0.3               | V    |

| $V_{CC}^2$             | $V_{EE}$              | -0.3     | +26.4              | V    |

| $V_{\mathrm{DD}}$      | DGND                  | 0        | +7                 | V    |

| AGND                   | DGND                  | -1       | +1                 | V    |

| AIN, REF <sub>IN</sub> | AGND                  | $V_{EE}$ | $V_{CC}$           | V    |

| Digital Inputs         | DGND                  | -0.5     | +7                 | V    |

| Digital Outputs        | DGND                  | -0.5     | $V_{\rm DD} + 0.3$ | V    |

| Max Junction           |                       |          |                    |      |

| Temperature            |                       |          | 175                | °C   |

| Specification       | With<br>Respect<br>To | Min | Max  | Unit |

|---------------------|-----------------------|-----|------|------|

| Operating           |                       |     |      |      |

| Temperature         |                       |     |      |      |

| J and K Grades      |                       | 0   | 70   | °C   |

| A and B Grades      |                       | -40 | +85  | °C   |

| S and T Grades      |                       | -55 | +125 | °C   |

| Storage Temperature |                       | -65 | +150 | °C   |

| Lead Temperature    |                       |     |      |      |

| (10 sec max)        |                       |     | 300  | °C   |

#### NOTES

#### ORDERING GUIDE1

| Model Package                        |                      | Temperature<br>Range | Tested and Specified | Package<br>Option <sup>2</sup> |

|--------------------------------------|----------------------|----------------------|----------------------|--------------------------------|

| AD679JN                              | 28-Pin Plastic DIP   | 0°C to +70°C         | AC                   | N-28                           |

| AD679KN                              | 28-Pin Plastic DIP   | 0°C to +70°C         | AC + DC              | N-28                           |

| AD679JD                              | 28-Pin Ceramic DIP   | 0°C to +70°C         | AC                   | D-28                           |

| AD679KD                              | 28-Pin Ceramic DIP   | 0°C to +70°C         | AC + DC              | D-28                           |

| AD679AD                              | 28-Pin Ceramic DIP   | -40°C to +85°C       | AC                   | D-28                           |

| AD679BD                              | 28-Pin Ceramic DIP   | -40°C to +85°C       | AC + DC              | D-28                           |

| AD679SD                              | 28-Pin Ceramic DIP   | −55°C to +125°C      | AC                   | D-28                           |

| AD679TD                              | 28-Pin Ceramic DIP   | −55°C to +125°C      | AC + DC              | D-28                           |

| AD679AJ                              | 44-Lead Ceramic JLCC | -40°C to +85°C       | AC                   | J-44                           |

| AD679BJ<br>AD679SD/883B <sup>3</sup> | 44-Lead Ceramic JLCC | −40°C to +85°C       | AC + DC              | J-44                           |

#### NOTES

#### **CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD679 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

REV. D –5–

<sup>&</sup>lt;sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

$<sup>^2</sup>$ The AD679 is not designed to operate from  $\pm 15$  V supplies.

<sup>&</sup>lt;sup>1</sup>For parallel read (14-bits) interface to 16-bit buses, see AD779.

<sup>&</sup>lt;sup>2</sup>N = Plastic DIP; D = Ceramic DIP; J = J-Leaded Ceramic Chip Carrier.

<sup>&</sup>lt;sup>3</sup>For details, grade, and package offerings screened in accordance with MIL-STD-883, refer to the

Analog Devices Military Products Databook or the current AD679/883B data sheet.

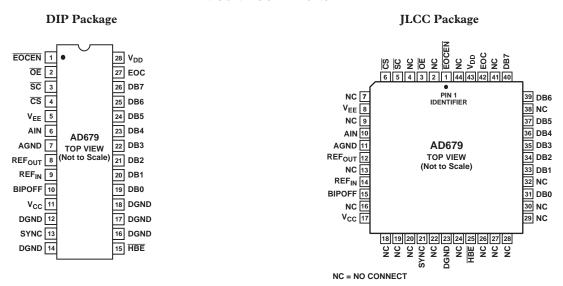

#### PIN CONFIGURATIONS

#### PIN FUNCTION DESCRIPTIONS

| Mnemonic               | 28-Lead<br>DIP<br>Pin No. | 44-Lead<br>JLCC<br>Pin No.                                                             | Type | Name and Function                                                                                                                                                                                                                                                                                                                                          |

|------------------------|---------------------------|----------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND                   | 7                         | 11                                                                                     | P    | Analog Ground. This is the ground return for AIN only.                                                                                                                                                                                                                                                                                                     |

| AIN                    | 6                         | 10                                                                                     | AI   | Analog Signal Input.                                                                                                                                                                                                                                                                                                                                       |

| BIPOFF                 | 10                        | 15                                                                                     | AI   | Bipolar Offset. Connect to AGND for $\pm 10$ V input unipolar mode and straight binary output coding. Connect to REF <sub>OUT</sub> for $\pm 5$ V input bipolar mode and twos complement binary output coding.                                                                                                                                             |

| CS                     | 4                         | 6                                                                                      | DI   | Chip Select. Active LOW.                                                                                                                                                                                                                                                                                                                                   |

| DGND                   | 12, 14                    | 23                                                                                     | P    | Digital Ground.                                                                                                                                                                                                                                                                                                                                            |

| DB7–DB0                | 26–19                     | 40, 39, 37, 36, 35, 34, 33, 31                                                         | DO   | Data Bits. These pins provide all 14 bits in two bytes (8 + 6 bits). Active HIGH.                                                                                                                                                                                                                                                                          |

| EOC                    | 27                        | 42                                                                                     | DO   | End-of-Convert. EOC goes LOW when a conversion starts and goes HIGH when the conversion finishes. In asynchronous mode, EOC is an open-drain output and requires an external 3 k $\Omega$ pull-up resistor. See $\overline{\text{EOCEN}}$ and SYNC pins for information on EOC gating.                                                                     |

| <b>EOCEN</b>           | 1                         | 1                                                                                      | DI   | End-of-Convert Enable. Enables EOC pin. Active LOW.                                                                                                                                                                                                                                                                                                        |

| HBE                    | 15                        | 25                                                                                     | DI   | High Byte Enable. If LOW, output contains high byte. If HIGH, output                                                                                                                                                                                                                                                                                       |

| 1100                   |                           |                                                                                        |      | contains low byte (corresponding to the most recently read high byte).                                                                                                                                                                                                                                                                                     |

| $\overline{\text{OE}}$ | 2                         | 3                                                                                      | DI   | Output Enable. A down-going transition on $\overline{OE}$ enables DB7 to DB0. Gated                                                                                                                                                                                                                                                                        |

| with                   | _                         |                                                                                        |      | CS. Active LOW.                                                                                                                                                                                                                                                                                                                                            |

| $REF_{IN}$             | 9                         | 14                                                                                     | AI   | Reference Input. 5 V input gives 10 V full-scale range.                                                                                                                                                                                                                                                                                                    |

| $REF_{OUT}$            | 8                         | 12                                                                                     | AO   | 5 V Reference Output. Tied to REF <sub>IN</sub> for normal operation.                                                                                                                                                                                                                                                                                      |

| $\overline{SC}$        | 3                         | 5                                                                                      | DI   | Start Convert. Active LOW. See SYNC pin for gating.                                                                                                                                                                                                                                                                                                        |

| SYNC                   | 13                        | 21                                                                                     | DI   | SYNC Control. If tied to $V_{DD}$ (synchronous mode), $\overline{SC}$ and $\overline{EOCEN}$ are gated by $\overline{CS}$ . If tied to DGND (asynchronous mode), $\overline{SC}$ and $\overline{EOCEN}$ are independent of $\overline{CS}$ , and EOC is an open-drain output. EOC requires an external 3 k $\Omega$ pull-up resistor in asynchronous mode. |

| $V_{CC}$               | 11                        | 17                                                                                     | P    | 12 V Analog Power.                                                                                                                                                                                                                                                                                                                                         |

| $V_{EE}$               | 5                         | 8                                                                                      | P    | -12 V Analog Power.                                                                                                                                                                                                                                                                                                                                        |

| $V_{ m DD}$            | 28                        | 43                                                                                     | P    | 5 V Digital Power.                                                                                                                                                                                                                                                                                                                                         |

| _                      | 16                        |                                                                                        | U    | Tie to DGND.                                                                                                                                                                                                                                                                                                                                               |

| _                      | 17–18                     | 2, 4, 7, 9, 13,<br>16, 18, 19, 20,<br>22, 24, 26, 27,<br>28, 29, 30, 32,<br>38, 41, 44 | U    | These pins are unused and should be connected to DGND or $V_{\rm DD}$ .                                                                                                                                                                                                                                                                                    |

Type: AI = Analog Input. AO = Analog Output. DI = Digital Input (TTL and 5 V CMOS compatible). DO = Digital Output (TTL and 5 V CMOS compatible). All DO pins are three-state drivers. P = Power. U = Unused.

#### **DEFINITIONS OF SPECIFICATIONS**

#### **Nyquist Frequency**

An implication of the Nyquist sampling theorem, the Nyquist frequency of a converter is the input frequency that is one-half the sampling frequency of the converter.

#### Signal-to-Noise and Distortion (S/N+D) Ratio

S/N+D is the ratio of the rms value of the measured input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc.

#### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of the first six harmonic components to the rms value of a full-scale input signal and is expressed as a percentage or in decibels. For input signals or harmonics above the Nyquist frequency, the aliased component is used.

#### Peak Spurious or Peak Harmonic Component

The peak spurious or peak harmonic component is the largest spectral component excluding the input signal and dc. This value is expressed in decibels relative to the rms value of a full-scale input signal.

#### Intermodulation Distortion (IMD)

With inputs consisting of sine waves at two frequencies, fa and fb, any device with nonlinearities will create distortion products, of order (m+n) at sum and difference frequencies of mfa  $\pm$  nfb, where m, n = 0, 1, 2, 3.... Intermodulation terms are those for which m or n is not equal to zero. For example, the second order terms are (fa+fb) and (fa-fb) and the third order terms are (2 fa+fb), (2 fa-fb), (fa+2 fb) and (fa-2 fb). The IMD products are expressed as the decibel ratio of the rms sum of the measured input signals to the rms sum of the distortion terms. The two signals applied to the converter are of equal amplitude, and the peak value of their sum is -0.5 dB from full-scale (9.44 V p-p). The IMD products are normalized to a 0 dB input signal.

#### Bandwidth

The full-power bandwidth is the input frequency at which the amplitude of the reconstructed fundamental is reduced by 3 dB for a full-scale input.

The full-linear bandwidth is the input frequency at which the slew rate limit of the sample-and-hold amplifier (SHA) is reached. At this point, the amplitude of the reconstructed fundamental has degraded by less than -0.1 dB. Beyond this frequency, distortion of the sampled input signal increases significantly.

The AD679 has been designed to optimize input bandwidth, allowing it to undersample input signals with frequencies significantly above the converter's Nyquist frequency.

#### **Aperture Delay**

Aperture delay is a measure of the SHA's performance and is measured from the falling edge of start convert  $(\overline{SC})$  to when the input signal is held for conversion. In synchronous mode, chip select  $(\overline{CS})$  should be LOW before  $\overline{SC}$  to minimize aperture delay.

#### **Aperture Jitter**

Aperture jitter is the variation in aperture delay for successive samples and is manifested as noise on the input to the A/D.

#### **Input Setting Time**

Settling time is a function of the SHA's ability to track fast slewing signals. This is specified as the maximum time required in track mode after a full-scale step input to guarantee rated conversion accuracy.

#### Differential Nonlinearity (DNL)

In an ideal ADC, code transitions are 1 LSB apart. Differential linearity is the deviation from this ideal value. It is often specified in terms of resolution for which no missing codes (NMC) are guaranteed.

#### Integral Nonlinearity (INL)

The ideal transfer function for a linear ADC is a straight line drawn between zero and full scale. The point used as zero occurs 1/2 LSB before the first code transition. Full scale is defined as a level 1 1/2 LSB beyond the last code transition. Integral linearity error is the worst case deviation of a code from the straight line. The deviation of each code is measured from the middle of that code.

Note that the linearity error is not user adjustable.

#### **Power Supply Rejection**

Variations in power supply will affect the full-scale transition, but not the converter's linearity. Power Supply Rejection is the maximum change in the full-scale transition point due to a change in power supply voltage from the nominal value.

#### **Temperature Drift**

This is the maximum change in the parameter from the initial value (@  $25^{\circ}$ C) to the value at  $T_{MIN}$  or  $T_{MAX}$ .

#### Unipolar Zero Error

In unipolar mode, the first transition should occur at a level 1/2 LSB above analog ground. Unipolar zero error is the deviation of the actual transition from that point. This error can be adjusted as discussed in the Input Connections and Calibration section.

#### Bipolar Zero Error

#### **Gain Error**

The last transition should occur at an analog value 1 1/2 LSB below the nominal full scale (9.9991 V for a 0 V to 10 V range, 4.9991 V for a  $\pm 5$  V range). The gain error is the deviation of the actual level at the last transition from the ideal level with the zero error trimmed out. This error can be adjusted as shown in the Input Connections and Calibration section.

REV. D –7–

## **AD679**—Typical Performance Characteristics

TPC 1. Harmonic Distortion vs. Input Frequency (–0.5 dB Input)

TPC 2. Total Harmonic Distortion vs. Input Frequency and Amplitude

TPC 3. S/(N+D) vs. Input Frequency and Amplitude

TPC 4. 5-Plot Averaged 2048 Point FFT at 128 kSPS,  $f_{\rm IN} = 10.009~{\rm kHz}$

TPC 5. Nonaveraged IMD Plot for  $f_{\rm IN}$  = 9.08 kHz ( $f_{\rm a}$ ), 9.58 kHz ( $f_{\rm b}$ ) at 128 kSPS

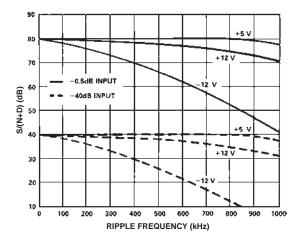

TPC 6. Power Supply Rejection ( $f_{IN} = 10 \text{ kHz}$ ,  $f_{SAMPLE} = 128 \text{ kSPS}$ ,  $V_{RIPPLE} = 0.1 \text{ V p-p}$ )

–8– REV. D

#### **CONVERSION CONTROL**

In synchronous mode (SYNC = HIGH), both chip select  $(\overline{CS})$  and start convert  $(\overline{SC})$  must be brought LOW to start a conversion.  $\overline{CS}$  should be LOW  $t_{SC}$  before  $\overline{SC}$  is brought LOW. In asynchronous mode (SYNC = LOW), a conversion is started by bringing  $\overline{SC}$  low, regardless of the state of  $\overline{CS}$ .

Before a conversion is started, end-of-convert (EOC) is HIGH and the sample-and-hold is in track mode. After a conversion is started, the sample-and-hold goes into hold mode and EOC goes LOW, signifying that a conversion is in progress. During the conversion, the sample-and-hold will go back into track mode and start acquiring the next sample.

In track mode, the sample-and-hold will settle to  $\pm 0.003\%$  (14 bits) in 1.5  $\mu s$  maximum. The acquisition time does not affect the throughput rate as the AD679 goes back into track mode more than 2  $\mu s$  before the next conversion. In multichannel systems, the input channel can be switched as soon as EOC goes LOW.

Bringing  $\overline{OE}$  LOW  $t_{OE}$  after  $\overline{CS}$  goes LOW makes the output register contents available on the output data bits (DB7–DB0). A period of time,  $t_{CD}$ , is required after  $\overline{OE}$  is brought HIGH before the next SC instruction is issued.

If  $\overline{SC}$  is held LOW, conversion accuracy may deteriorate. For this reason,  $\overline{SC}$  should not be held low in an attempt to operate in a continuously converting mode.

**Table I. Start Conversion Truth Table**

|                      | SYNC        | Inputs<br>CS  | <u>SC</u>   | Status                                                                          |

|----------------------|-------------|---------------|-------------|---------------------------------------------------------------------------------|

| Synchronous<br>Mode  | 1 1         | 1 0           | X<br>Ł      | No Conversion<br>Start Conversion                                               |

|                      | 1           | <b>1</b><br>0 | 0           | Start Conversion (Not Recommended) Continuous Conversion (Not Recommended)      |

| Asynchronous<br>Mode | 0<br>0<br>0 | X<br>X<br>X   | 1<br>1<br>0 | No Conversion<br>Start Conversion<br>Continuous Conversion<br>(Not Recommended) |

<sup>1 =</sup> HIGH voltage level.

Table II. 14-Bit Mode Coding Format (1 LSB = 0.61 mV)

| Unipolar Co<br>(Straight B          | _                       | Bipolar Coding<br>(Twos Complement)                     |                                           |  |  |  |

|-------------------------------------|-------------------------|---------------------------------------------------------|-------------------------------------------|--|--|--|

| V <sub>IN</sub> * Output Code       |                         | V <sub>IN</sub> * (V)                                   | Output Code                               |  |  |  |

| 0.00000 V<br>5.00000 V<br>9.99939 V | 000 0<br>100 0<br>111 1 | -5.00000<br>-0.00061<br>0.00000<br>+2.50000<br>+4.99939 | 100 0<br>111 1<br>000 0<br>010 0<br>011 1 |  |  |  |

<sup>\*</sup>Code center.

#### **END-OF-CONVERT**

In asynchronous mode, end-of-convert (EOC) is an open-drain output (requiring a minimum 3  $k\Omega$  pull-up resistor) enabled by end-of-convert enable  $\overline{(EOCEN)}$ . In synchronous mode, EOC is a three-state output that is enabled by  $\overline{EOCEN}$  and  $\overline{CS}$ . See Table III. Access  $(t_{BA})$  and float  $(t_{FD})$  timing specifications do not apply in asynchronous mode where they are a function of the time constant formed by the external load capacitance and the pull-up resistor.

#### **OUTPUT ENABLE OPERATION**

The data bits (DB7–DB0) are three-state outputs that are enabled by chip select  $(\overline{CS})$  and output enable  $(\overline{OE})$ .  $\overline{CS}$  should be LOW  $t_{OE}$  before  $\overline{OE}$  is brought LOW.

When EOC goes HIGH, the conversion is completed and the output data may be read. The output is read in two steps as a 16-bit word, with the high byte read first, followed by the low byte. High byte enable (HBE) controls the output sequence. The 14-bit result is left justified within the 16-bit field.

In unipolar mode (BIPOFF tied to AGND), the output coding is straight binary. In bipolar mode (BIPOFF tied to REF<sub>OUT</sub>), output coding is twos complement binary.

#### **POWER-UP**

The AD679 typically requires 10  $\mu s$  after power-up to reset internal logic.

Table III. Conversion Status Truth Table

|              |   | Inpu<br>CS | EOCEN | Output<br>EOC | Status         |

|--------------|---|------------|-------|---------------|----------------|

| Synchronous  | 1 | 0          | 0     | 0             | Converting     |

| Mode         | 1 | 0          | 0     | 1             | Not Converting |

|              | 1 | 1          | X     | High Z        | Either         |

|              | 1 | X          | 1     | High Z        | Either         |

| Asynchronous | 0 | X          | 0     | 0             | Converting     |

| Mode*        | 0 | X          | 0     | High Z        | Not Converting |

|              | 0 | X          | 1     | High Z        | Either         |

<sup>1 =</sup> HIGH voltage level.

Table IV. Output Enable Truth Table

|                        | Inputs (CS U OE) |     | Outputs<br>DB7 DB0                             |

|------------------------|------------------|-----|------------------------------------------------|

|                        | X                | 1   | $\leftarrow \operatorname{High} Z \rightarrow$ |

| Unipolar or<br>Bipolar | 0<br>1           | 0 0 | abcdefgh<br>ijklmn00                           |

<sup>1 =</sup> HIGH voltage level.

Data coding is binary for unipolar mode and twos complement binary for bipolar mode.

REV. D –9–

<sup>0 =</sup> LOW voltage level.

X = Don't care.

<sup>ightharpoonup = HIGH</sup> to LOW transition. Must stay low for t = t<sub>CP</sub>.

<sup>0 =</sup> LOW voltage level.

X = Don't care.

<sup>\*</sup>EOC requires a pull-up resistor in asynchronous mode.

rel. a = MSB.

<sup>0 =</sup> LOW voltage level. n = LSB.

X = Don't care.

U = Logical OR.

#### INPUT CONNECTIONS AND CALIBRATION

The high (10 M $\Omega$ ) input impedance of the AD679 eases the task of interfacing to high source impedances or multiplexer channel-to-channel mismatches of up to 300  $\Omega$ . The 10 V p-p full-scale input range accepts the majority of signal voltages without the need for voltage divider networks that could deteriorate the accuracy of the ADC.

The AD679 is factory trimmed to minimize offset, gain, and linearity errors. In unipolar mode, the only external component that is required is a 50  $\Omega$  ±1% resistor. Two resistors are required in bipolar mode. If offset and gain are not critical (as in some ac applications), even these components can be eliminated.

In some applications, offset and gain errors need to be trimmed out completely. The following sections describe the correct procedure for these various situations.

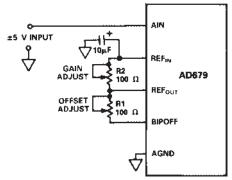

#### **Bipolar Range Inputs**

The connections for the bipolar mode are shown in Figure 5. In this mode, data output coding is twos complement binary. This circuit allows approximately  $\pm 25$  mV of offset trim range ( $\pm 40$  LSB) and  $\pm 0.5\%$  of gain trim range ( $\pm 80$  LSB).

Either or both of the trim pots can be replaced with  $50 \Omega \pm 1\%$  fixed resistors if the AD679 accuracy limits are sufficient for application. If the pins are shorted together, the additional offset and gain error is approximately 80 LSB.

To trim bipolar zero to its nominal value, apply a signal 1/2 LSB below midrange (-0.305 mV for a  $\pm 5$  V range) and adjust R1 until the major carry transition is located (11 1111 1111 1111 to 00 0000 0000 0000). To trim the gain, apply a signal 1 1/2 LSB below full scale (+4.9991 V for a  $\pm 5$  V range) and adjust R2 to give the last positive transition (01 1111 1111 1110 to 01 1111 1111 1111). These trims are interactive so several iterations may be necessary for convergence.

A single pass calibration can be done by substituting a bipolar offset trim (error at minus full scale) for the bipolar zero trim (error at midscale) using the same circuit. First, apply a signal 1/2 LSB above minus full scale (–4.9997 V for a  $\pm 5$  V range) and adjust R1 until the minus full-scale transition is located (10 0000 0000 0000 to 10 000 0000 0001). Then perform the gain error trim as outlined above.

Figure 5. Bipolar Input Connections with Gain and Offset Trims

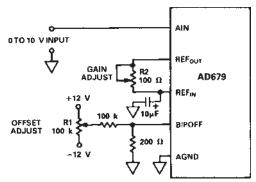

#### **Unipolar Range Inputs**

Offset and gain errors can be trimmed out by using the configuration shown in Figure 6. This circuit allows approximately  $\pm 25$  mV of offset trim range ( $\pm 40$  LSB) and  $\pm 0.5\%$  of gain trim range ( $\pm 80$  LSB).

The gain trim is done by adjusting R2. If the nominal value is required, apply a signal 1 1/2 LSB below full scale (9.9997 V for a 10 V range) and adjust R2 until the last transition is located (11 1111 1111 1110 to 11 1111 1111 1111).

If offset adjustment is not required, BIPOFF should be connected directly to AGND. If gain adjustment is not required, R2 should be replaced with a fixed 50  $\Omega$   $\pm 1\%$  metal film resistor. If REF $_{OUT}$  is connected directly to REF $_{IN}$ , the additional gain error is approximately 1%.

Figure 6. Unipolar Input Connections with Gain and Offset Trims

#### REFERENCE DECOUPLING

It is recommended that a 10  $\mu$ F tantalum capacitor be connected between REF<sub>IN</sub> (Pin 9) and ground. This has the effect of improving the S/N+D ratio through filtering possible broadband noise contributions from the voltage reference.

#### **BOARD LAYOUT**

Designing with high resolution data converters requires careful attention to board layout. Trace impedance is a significant issue. A 1.22 mA current through a 0.5  $\Omega$  trace will develop a voltage drop of 0.6 mV, which is 1 LSB at the 14-bit level for a 10 V full-scale span. In addition to ground drops, inductive and capacitive coupling need to be considered, especially when high accuracy analog signals share the same board with digital signals. Finally, power supplies need to be decoupled in order to filter out ac noise.

Analog and digital signals should not share a common path. Each signal should have an appropriate analog or digital return routed close to it. Using this approach, signal loops enclose a small area, minimizing the inductive coupling of noise. Wide PC tracks, large gauge wire, and ground planes are highly recommended to provide low impedance signal paths. Separate analog

–10– REV. D

and digital ground planes are also desirable, with a single interconnection point to minimize ground loops. Analog signals should be routed as far as possible from digital signals and should cross them at right angles.

The AD679 incorporates several features to help the user's layout. Analog pins ( $V_{EE}$ , AIN, AGND, REF<sub>OUT</sub>, REF<sub>IN</sub>, BIPOFF,  $V_{CC}$ ) are adjacent to help isolate analog from digital signals. In addition, the 10 M $\Omega$  input impedance of AIN minimizes input trace impedance errors. Finally, ground currents have been minimized by careful circuit architecture. Current through AGND is 200  $\mu$ A, with no code dependent variation. The current through DGND is dominated by the return current for DB7–DB0 and EOC.

#### **SUPPLY DECOUPLING**

The AD679 power supplies should be well filtered, well regulated, and free from high frequency noise. Switching power supplies are not recommended due to their tendency to generate spikes that can induce noise in the analog system.

Decoupling capacitors should be used in very close layout proximity between all power supply pins and analog ground. A 10  $\mu F$  tantalum capacitor in parallel with a 0.1  $\mu F$  ceramic capacitor provides adequate decoupling.

An effort should be made to minimize the trace length between the capacitor leads and the respective converter power supply and common pins. The circuit layout should attempt to locate the AD679, associated analog input circuitry, and interconnections as far as possible from logic circuitry. A solid analog ground plane around the AD679 isolates large switching ground currents. For these reasons, the use of wire wrap circuit construction is not recommended; careful printed circuit construction is preferred.

#### **GROUNDING**

If a single AD679 is used with separate analog and digital ground planes, connect the analog ground plane to AGND and the digital ground plane to DGND, keeping lead lengths as short as possible. Then connect AGND and DGND together at the AD679. If multiple AD679s are used or if the AD679 shares analog supplies with other components, connect the analog and digital returns together once at the power supplies rather than at each chip. This prevents large ground loops, which inductively couple noise and allow digital currents to flow through the analog system.

#### USE OF EXTERNAL VOLTAGE REFERENCE

The AD679 features an on-chip voltage reference. For improved gain accuracy over temperature, a high performance external voltage reference may be used in place of the on-chip reference.

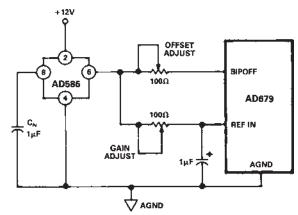

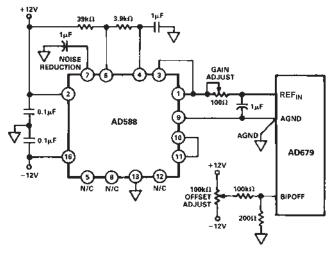

The AD586 and AD588 are popular references appropriate for use with high resolution converters. The AD586 is a low cost reference that utilizes a buried Zener architecture to provide low noise and drift. The AD588 is a higher performance reference that uses a proprietary implanted buried Zener diode in conjunction with laser-trimmed thin-film resistors for low offset and low drift.

Figure 7 shows the use of the AD586 with the AD679 in a bipolar input mode. Over the  $0^{\circ}$ C to  $70^{\circ}$ C range, the AD586 L-grade exhibits less than a 2.25 mV output change from its initial value at 25°C. REF<sub>IN</sub> (Pin 9) scales its input by a factor of two; thus, this change becomes effectively 4.5 mV. When applied to the AD679, this results in a total gain drift of 0.09% FSR, which is an improvement over the on-chip reference performance of 0.11% FSR. A noise-reduction capacitor,  $C_N$ , has been shown.

This capacitor reduces the broadband noise of the AD586 output, thereby optimizing the overall ac and dc performance of the AD679.

Figure 7. Bipolar Input with Gain and Offset Trims

Figure 8 shows the AD679 in unipolar input mode with the AD588 reference. The AD588 output is accurate to 0.65 mV from its value at 25°C over the 0°C to 70°C range. This results in a 0.06% FSR total gain drift for the AD679, a substantial improvement over the on-chip reference performance of 0.11% FSR. A noise-reduction network on Pins 4, 6, and 7 has been shown. The 1  $\mu F$  capacitors form low-pass filters with the internal resistance of the AD588 Zener and amplifier cells and external resistance. This reduces the high frequency (to 1 MHz) noise of the AD588, providing optimum ac and dc performance of the AD679.

Figure 8. Unipolar Input with Gain and Offset Trims

REV. D –11–

#### INTERFACING THE AD679 TO MICROPROCESSORS

The I/O capabilities of the AD679 allow direct interfacing to general-purpose and DSP microprocessor buses. The asynchronous conversion control feature allows complete flexibility and control with minimal external hardware.

The following examples illustrate typical AD679 interface configurations.

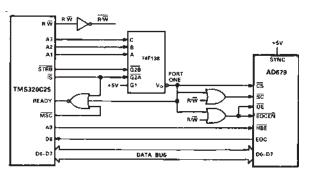

#### AD679 to TMS320C25

In Figure 9, the AD679 is mapped into the TMS320C25 I/O space. AD679 conversions are initiated by issuing an OUT instruction to Port 1. EOC status and the conversion result are read in with an IN instruction to Port 1. A single wait state is inserted by generating the processor READY input from  $\overline{\rm IS}$ , Port 1, and  $\overline{\rm MSC}$ . Address line A0 provides  $\overline{\rm HBE}$  decoding to select between the high and low bytes of data. This configuration supports processor clock speeds of 20 MHz and is capable of supporting processor clock speeds of 40 MHz if a NOP instruction follows each AD679 read instruction.

Figure 9. AD679 to TMS320C25 Interface

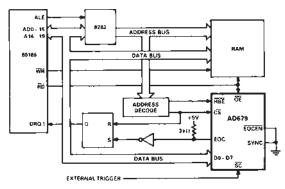

#### AD679 to 80186

Figure 10 shows the AD679 interfaced to the 80186 microprocessor. This interface allows the 80186's built-in DMA controller to transfer the AD679 output into a RAM based FIFO buffer of any length, with no microprocessor intervention.

In this application the AD679 is configured in the asynchronous mode, which allows conversions to be initiated by an external trigger source independent of the microprocessor clock. After each conversion, the AD679 EOC signal generates a DMA request to Channel 1 (DRQ1). The subsequent DMA READ sequences the high and low byte AD679 data and resets the interrupt latch. The system designer must assign a sufficient priority to the DMA channel to ensure that the DMA request is serviced before the next conversion is completed. This configuration can be used with 6 MHz and 8 MHz 80186 processors.

Figure 10. AD679 to 80186 DMA Interface

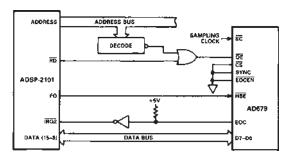

#### AD679 to Analog Devices ADSP-2101

Figure 11 demonstrates the AD679 interfaced to an ADSP-2101. With a clock frequency of 12.5 MHz, and instruction execution in one 80 ns cycle, the digital signal processor supports the AD679 interface with one wait state.

The converter is configured to run asynchronously using a sampling clock. The EOC output of the AD679 gets asserted at the end of each conversion and causes an interrupt. Upon interrupt, the ADSP-2101 immediately asserts its FO pin LOW. In the following cycle, the processor starts a data memory read by providing an address on the DMA bus. The decoded address generates  $\overline{\text{OE}}$  for the converter, and the high byte of the conversion result is read over the data bus. The read operation is extended with one wait state and thus started and completed within two processor cycles (160 ns). Next, the ADSP-2101 asserts its FO HIGH. This allows the processor to start reading the lower byte of data. This read operation executes in a similar manner to the first and is completed during the next 160 ns.

Figure 11. AD679 to ADSP-2101 Interface

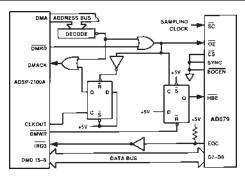

#### AD679 to Analog Devices ADSP-2100A

Figure 12 demonstrates the AD679 interfaced to an ADSP-2100A. With a clock frequency of 12.5 MHz, and instruction execution in one 80 ns cycle, the digital signal processor supports the AD679 data memory interface with three hardware wait states.

The converter is configured to run asynchronously using a sampling clock. The EOC output of the AD679 gets asserted at the end of each conversion and causes an interrupt. Upon interrupt, the ADSP-2100A immediately executes a data memory write instruction, which asserts  $\overline{HBE}$ . In the following cycle, the processor starts a data memory read (high byte read) by providing an address on the DMA bus. The decoded address generates  $\overline{OE}$  for the converter.  $\overline{OE}$ , together with logic and latch, is used to force the ADSP-2100A into a one cycle wait state by generating DMACK. The read operation is thus started and completed within two processor cycles (160 ns).  $\overline{HBE}$  is released during high byte read. This allows the processor to read the lower byte of data as soon as high byte read is complete. The low byte read operation executes in a similar manner to the first and is completed during the next 160 ns.

Figure 12. AD679 to ADSP-2100A Interface

REV. D –13–

#### **OUTLINE DIMENSIONS**

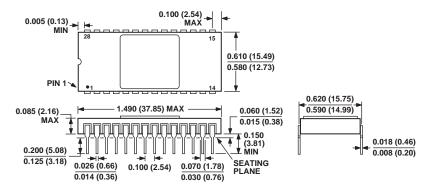

### 28-Lead Side-Brazed Ceramic Dual In-Line Package [SBDIP]

(D-28)

Dimensions shown in inches and (millimeters)

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

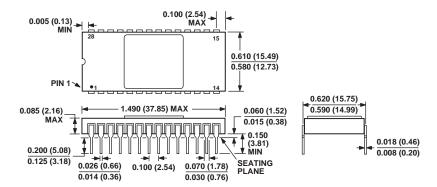

#### 28-Lead Plastic Dual In-Line Package [PDIP] Wide Body

(N-28)

Dimensions shown in inches and (millimeters)

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

–14– REV. D

#### **OUTLINE DIMENSIONS**

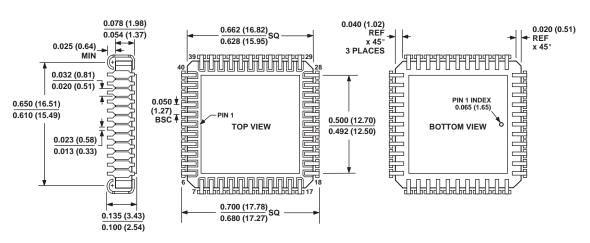

## 44-Lead Ceramic Leaded Chip Carrier, J-Formed Leads [JLCC] (J-44)

Dimensions shown in inches and (millimeters)

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETERS DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

## **Revision History**

| Location                                       | Page      |

|------------------------------------------------|-----------|

| 6/04—Data Sheet changed from REV. C to REV. D. |           |

| Updated Format                                 | Universal |

| Changes to FEATURES                            |           |

| Changes to AC SPECIFICATIONS                   |           |

| Changes to DC SPECIFICATIONS                   |           |

| Changes to ORDERING GUIDE                      | 5         |

| Updated OUTLINE DIMENSIONS                     |           |

REV. D –15–

### О компании

ООО "ТрейдЭлектроникс" - это оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов. Реализуемая нашей компанией продукция насчитывает более полумиллиона наименований.

Благодаря этому наша компания предлагает к поставке практически не ограниченный ассортимент компонентов как оптовыми, мелкооптовыми партиями, так и в розницу.

Наличие собственной эффективной системы логистики обеспечивает надежную поставку продукции по конкурентным ценам в точно указанные сроки.

Срок поставки со стоков в Европе и Америке – от 3 до 14 дней.

Срок поставки из Азии - от 10 дней.

Благодаря развитой сети поставщиков, помогаем в поиске и приобретении экзотичных или снятых с производства компонентов.

Предоставляем спец цены на элементы для создания инженерных сэмплов.

Упорный труд, качественный результат дают нам право быть уверенными в себе и надежными для наших клиентов.

#### Наша компания это:

- Гарантия качества поставляемой продукции

- Широкий ассортимент

- Минимальные сроки поставок

- Техническая поддержка

- Подбор комплектации

- Индивидуальный подход

- Гибкое ценообразование

Наша организация особенно сильна в поставках модулей, микросхем, пассивных компонентов, ксайленсах (XC), EPF, EPM и силовой электроники.

Большой выбор предлагаемой продукции, различные виды оплаты и доставки, позволят Вам сэкономить время и получить максимум выгоды от сотрудничества с нами!

### <u>Перечень производителей, продукцию которых мы поставляем</u> на российский рынок

**Panasonic**

RENESAS

гарантия бесперебойности производства и качества выпускаемой продукции

С удовольствием будем прорабатывать для Вас поставки всех необходимых компонентов по текущим запросам для скорейшего выявления групп элементов, по которым сотрудничество именно с нашей компанией будет для Вас максимально выгодным!

Менеджер отдела продаж ООО

«Трейд Электроникс»

Шишлаков Евгений

8 (495)668-30-28 доб 169

С уважением,

http://www.tradeelectronics.ru/

manager28@tradeelectronics.ru